The DIE configuration details of the upcoming Intel Xeon 5th Gen processor, codenamed Emerald Rapids, have emerged ahead of its scheduled release on December 14th (US time). Within the Emerald Rapids family, the top-tier offering is the Intel Xeon 8592+, boasting an impressive 64 cores and 128 threads, along with a substantial 480MB L3 Cache. Notably, this processor employs a pure P Cores design and adopts the Raptor Cove CPU architecture.

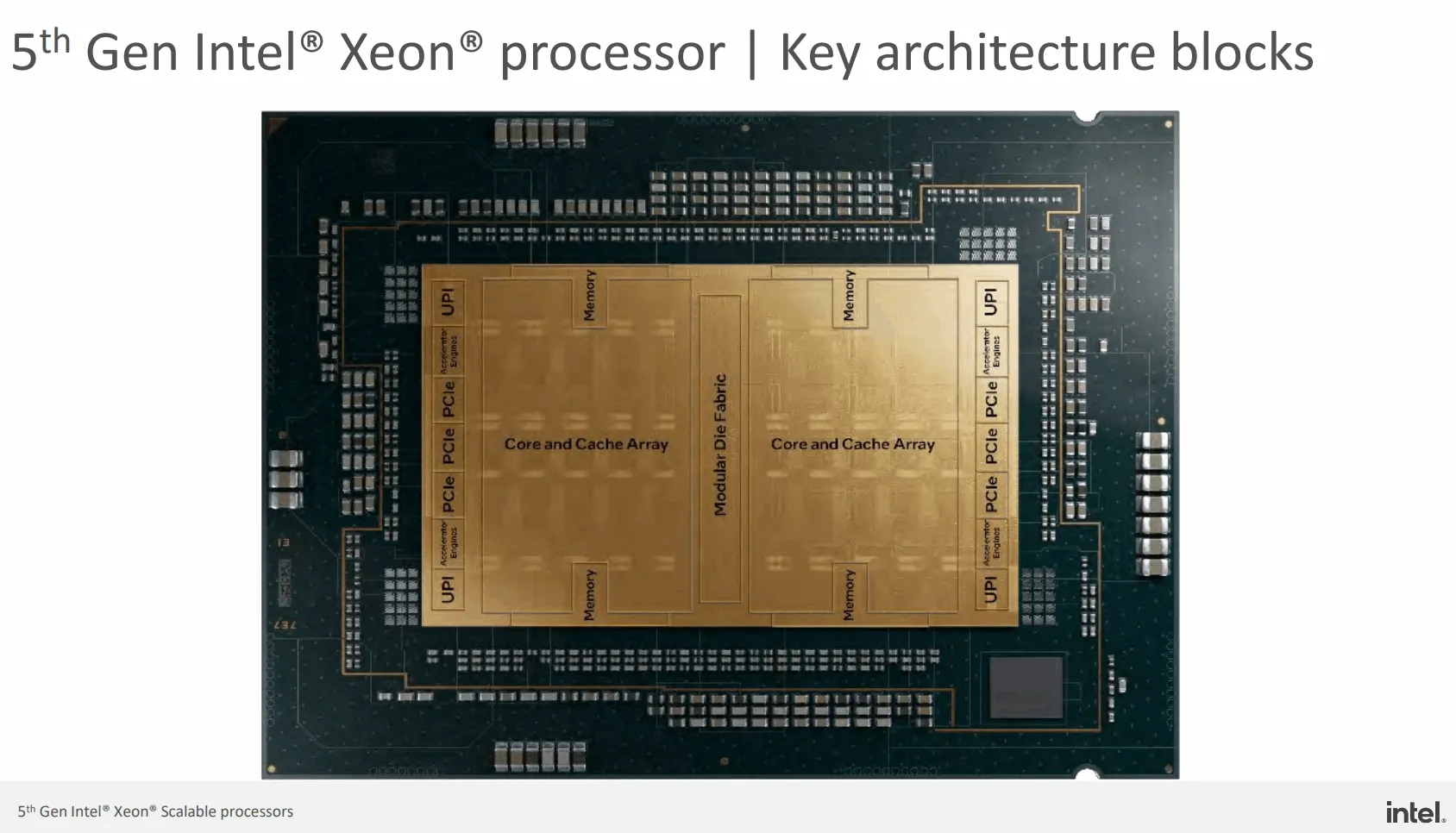

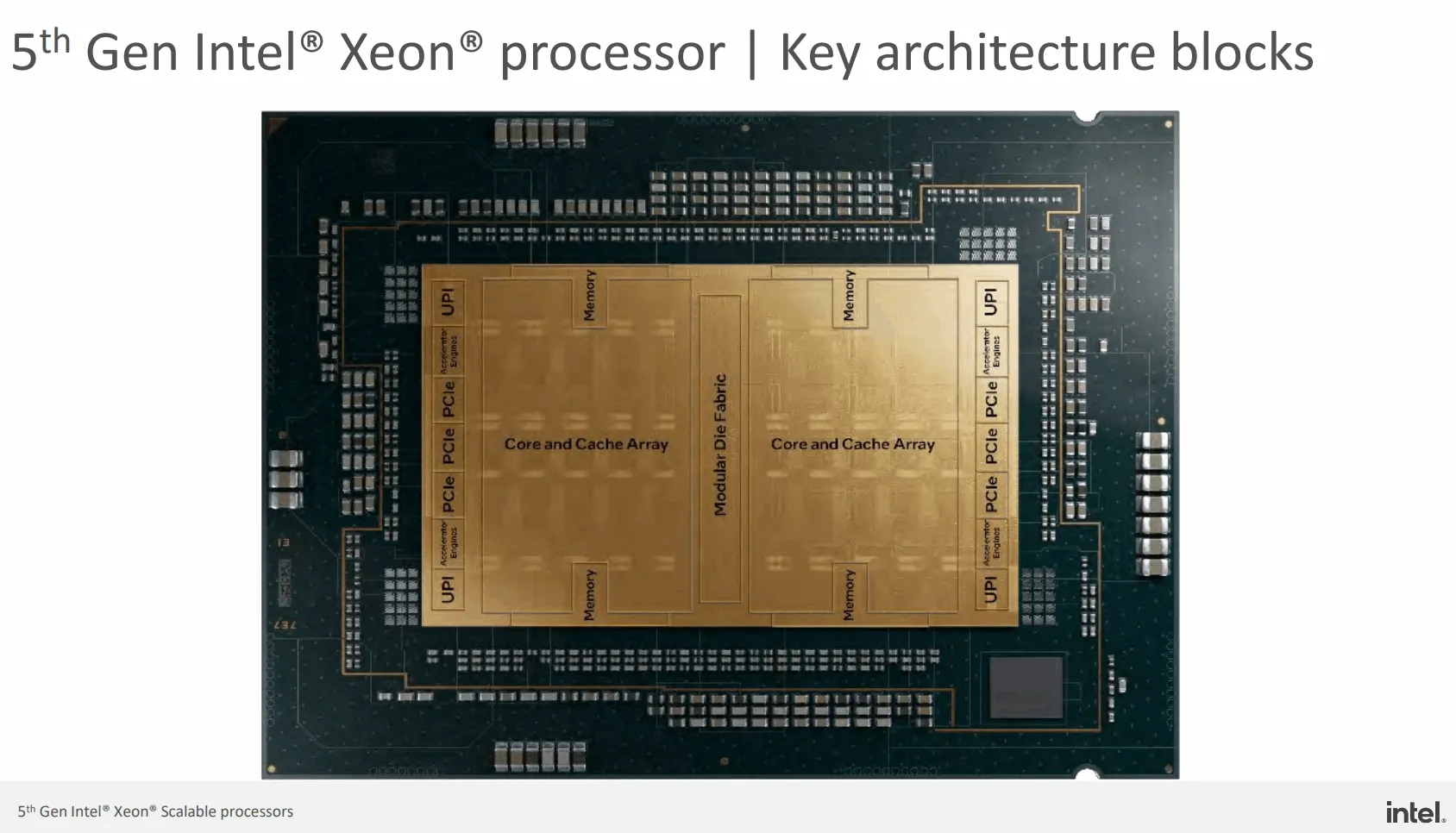

Compared to its predecessor, the Intel 4th Gen Xeon processor, Sapphire Rapids, Emerald Rapids introduces the Intel AMX engine, resulting in a notable 40% performance boost for AI applications. Each Emerald Rapids Chiplet can accommodate up to 35 cores, albeit with three cores disabled in certain configurations. Additionally, each Tile features two DDR5-5600 MT/s memory controllers, totaling four controllers and providing an 8-channel memory configuration.

Furthermore, each DIE incorporates three sets of PCIe controllers as you can see from the leaked PDF.

Emerald Rapids boasts support for Compute Express Link (CXL) Types 1, 2, and 3, offering an impressive 80 PCIe 5.0 lanes. It enhances Intel Ultra Path Interconnect (UPI) by introducing a UPI controller. In addition to significant AI enhancements, Emerald Rapids exhibits architectural improvements over its predecessor, Sapphire Rapids. Intel is set to unveil further details during an upcoming press conference on December 14th.