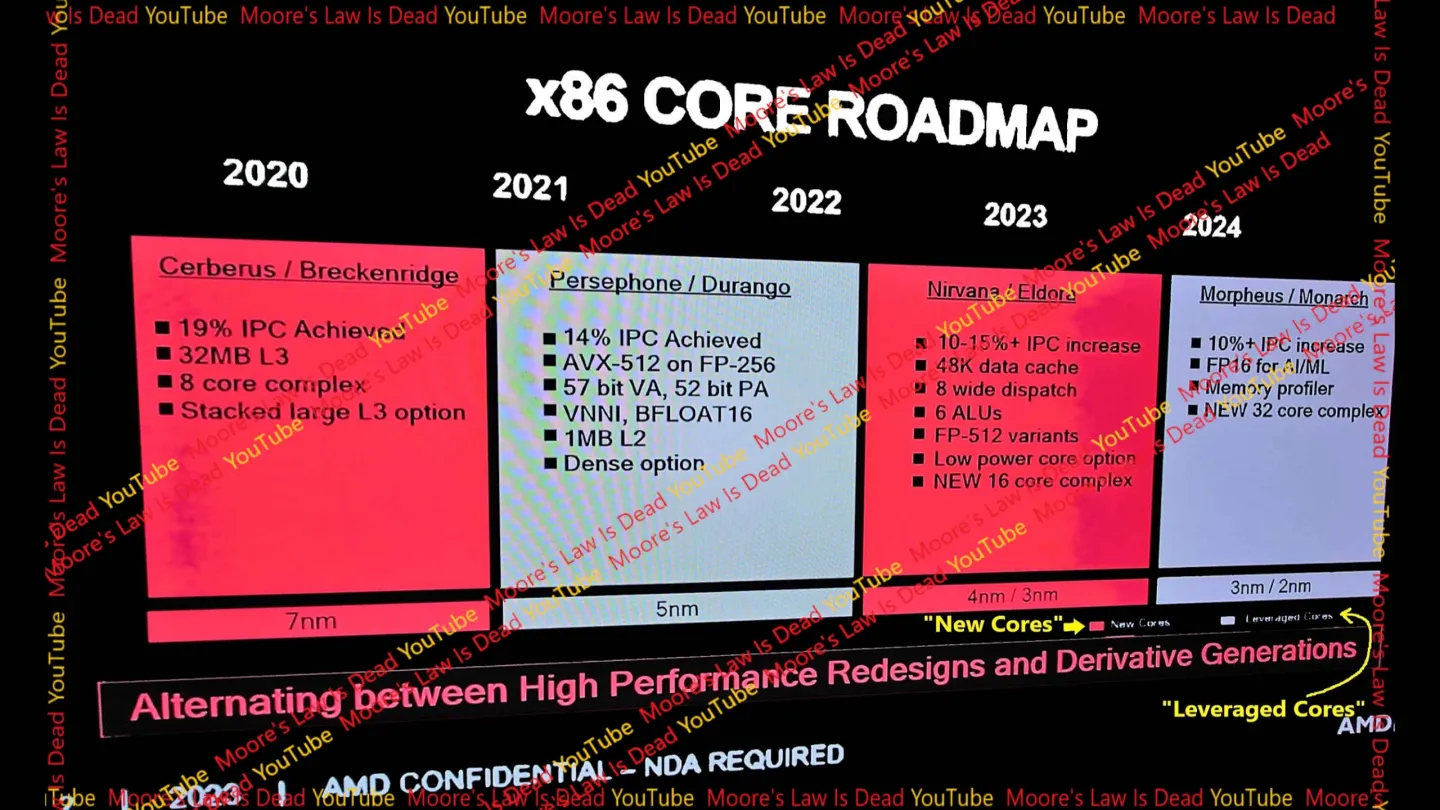

MLID has disclosed two slides obtained from an internal AMD presentation originally intended for internal use. These slides offer insights into the progress and strategies concerning the upcoming Zen architectures of the next generation. They divulge crucial details such as anticipated IPC enhancements, supported functionalities, and core quantities.

The roadmap has undergone a minor timeline adjustment. It's worth noting that these microarchitectures encompass a broad spectrum of products, including data center and consumer-oriented series. Consequently, release timelines may not align exclusively with AMD's plans for Ryzen 8000 and beyond but also take into consideration EPYC products.

Zen5 (Nirvana) - 2024

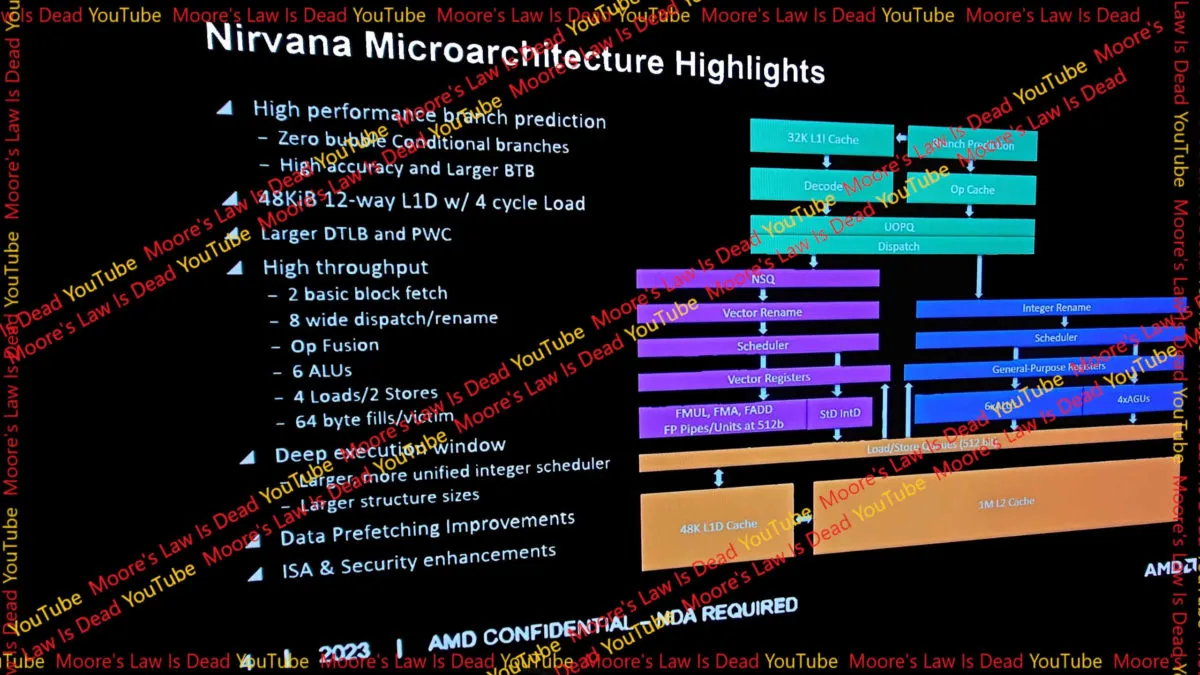

The new microarchitectures, utilizing 4nm/3nm technology, feature Nirvana (Zen5), targeting the Ryzen 8000 series. According to the slide, an expected IPC improvement of 10% to 15% is anticipated. However, it's crucial to emphasize that this figure remains unverified in retail silicon, as it represents a goal set by the presentation. Additionally, the slide delineates specifications, including a 48K data cache, 8 wide dispatches, 6 ALUs, FP-512 variants, and a novel low-power core option.

Notably, AMD has raised the maximum cores per CCX from 8 to 16. The precise configuration of this increase remains uncertain, whether it applies to the "Eldora" CCD with 16 cores within a single CCX or spreads across two CCXs with smaller L3 caches. AMD leverages the TSMC 4 nm EUV node for "Eldora," while the mobile processor based on "Zen 5" could potentially utilize the more advanced TSMC 3 nm EUV node.

Zen6 (Morpheus) - 2H 2025

Morpheus serves as the microarchitecture codename for Zen6, expected to utilize 3nm and 2nm process technology. AMD is targeting a 10% IPC increase over Nirvana. Furthermore, AMD intends to introduce FP16 instructions to accelerate AI/ML algorithms and a new memory profiler. Concerning the core complex, AMD plans to raise the core count to 32, which presumably applies to Zen6c, not Zen6.

There are hints, albeit unverified, that Zen6 might feature a chip layout redesign akin to Zen2, involving new packaging techniques, potentially entailing the stacking of CCDs on top of the IOD (input/output interface die). This would signify a significant departure from AMD's conventional disaggregated chiplet design approach. Whether Zen6 will utilize the AM5 socket remains pending confirmation.

Source: Videocardz