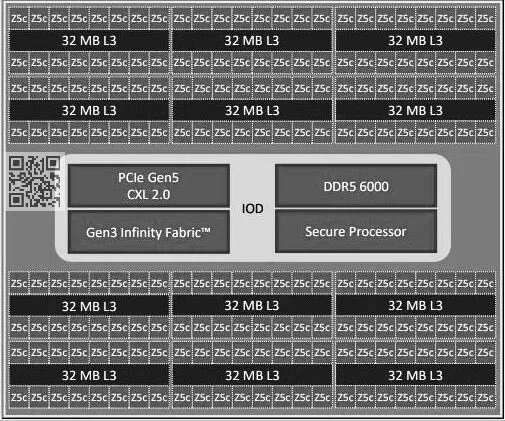

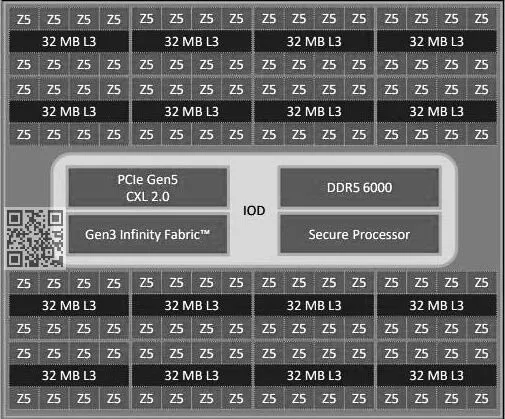

In its construction, the EPYC "Turin" integrates an updated server I/O die (sIOD), encircled by up to 16 CPU complex dies (CCDs). Anticipated to be manufactured using the TSMC N4P foundry node, this approach marks an advancement over the TSMC N4 node used for the "Phoenix" client processors and the TSMC N5 node for the Zen 4 CCDs. The N4P node is reported to enhance power efficiency by up to 22% compared to the N5 node, along with a 6% increase in transistor density.

Each Zen 5 CCD in the standard "Turin" configuration comprises 8 CPU cores, sharing 32 MB of L3 cache memory. The high-density variant for cloud data-centers, however, adopts a different approach. It utilizes 12 Zen 5c CCDs, which are a compact version of the Zen 5 core, maintaining similar instruction sets (ISA) and instructions per clock (IPC), but operating at lower clock speeds, suited for high core-count environments. This variant of the Multi-Chip Module (MCM) contains 12 Zen 5c CCDs, each with 16 cores sharing a 32 MB L3 cache. The Zen 5c CCD effectively doubles the available L3 cache compared to its predecessor, indicating potential improvements in performance and efficiency.

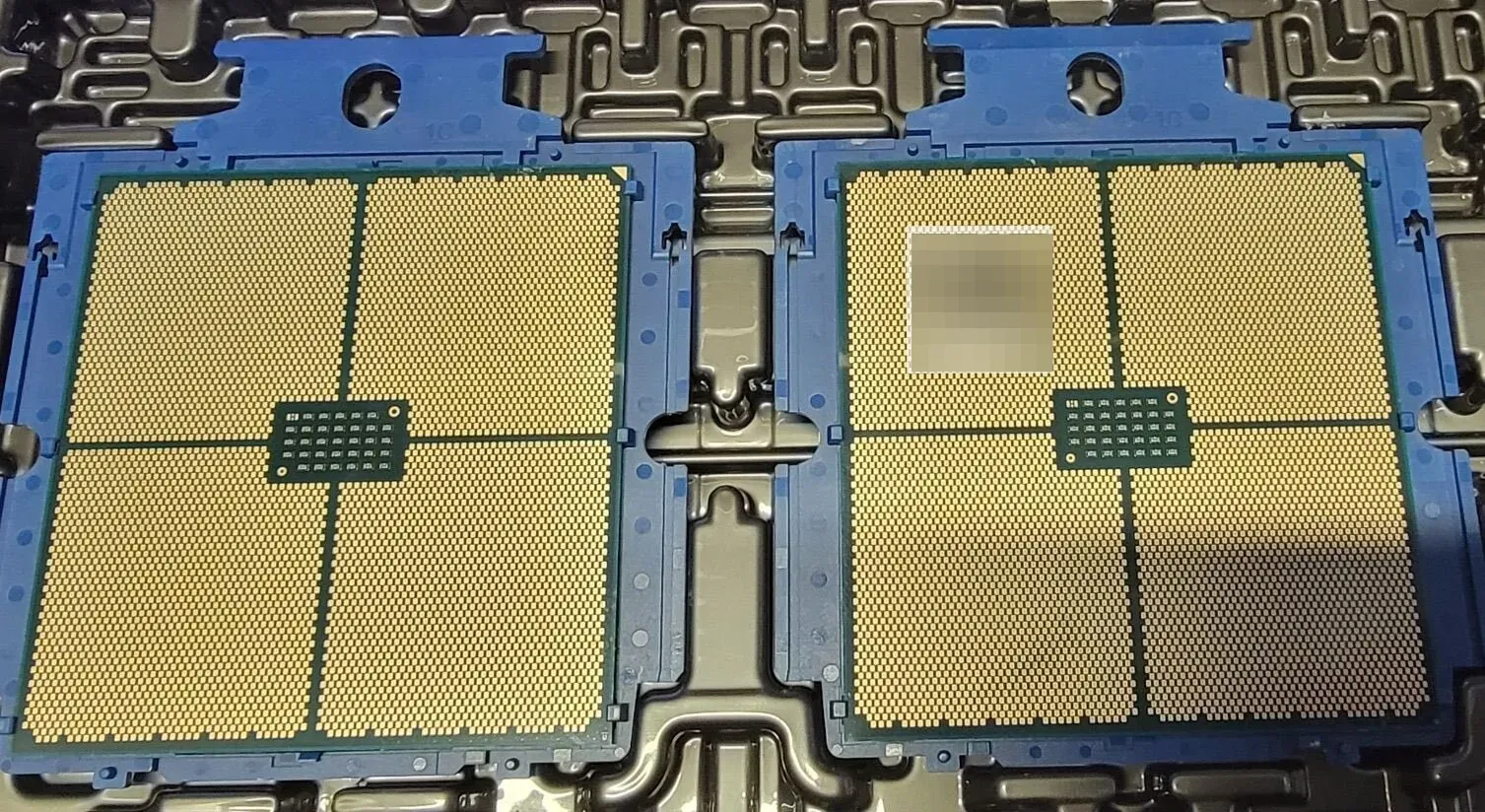

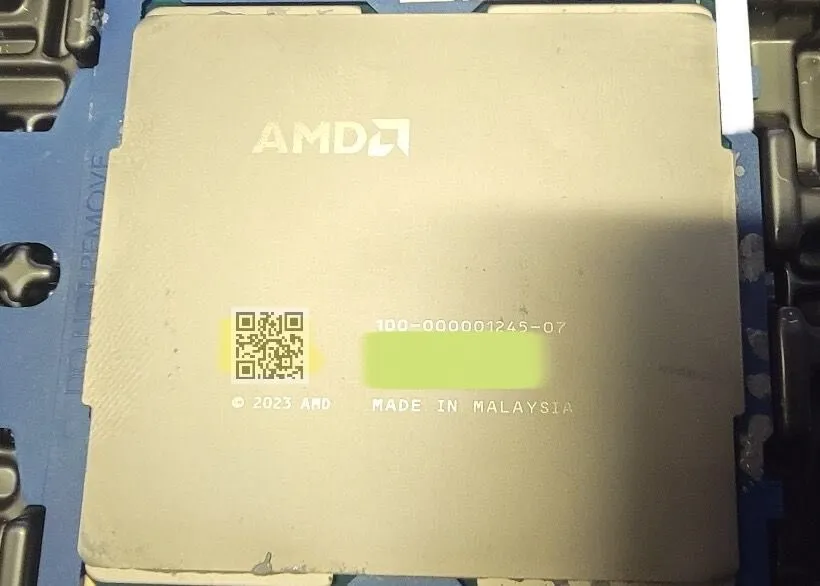

Sources: YuuKi_AnS (Twitter), VideoCardz