Introduction

ClockTuner v2.0 for Ryzen (CTR) Guide

Introduction

Hi guys! Before starting the review of the new Clock Tuner for Ryzen, I would like to thank the Ryzen community for their patience and warm welcome. The release of CTR 1.0 and 1.1 was not so smooth, and many users experienced a few problems and bugs which could not be fixed with a hotfix or patch. I wasn't blind to these problems, but it was impossible to handle so many requests physically. Despite all the difficulties, it was decided to re-create the project in a fairly short time without the proper support from the company’s giants. Even if some samples were provided (low and mid-end processors), there was no information support at all. Fortunately, people in the community had valuable information and skills, which made it possible to turn all plans into reality. In particular, special thanks to Keaton Blomquist and Vadym Kosmin for their contribution to the development of CTR 2.0.

- Download CTR and unpack the ZIP archive in a directory of your choice

- Then download the Cinebench R20 archive and extract the contents of the archive to the “CB20” folder (this folder is located inside the CTR folder).

ZEN3 potential

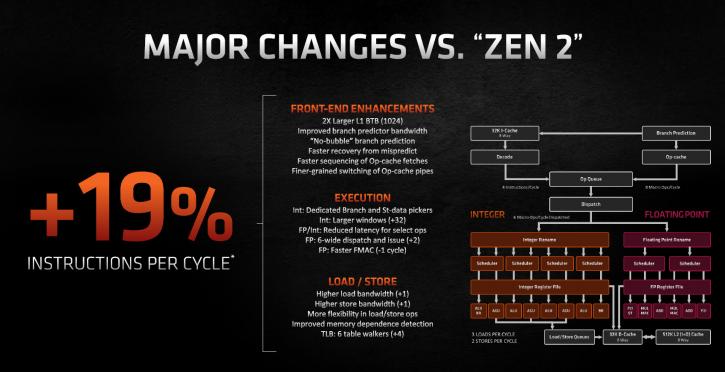

In addition to all of the above, there was another event with a capital letter, which added to the pleasant worries and delayed the release of CTR 2.0: the long-awaited release of AMD processors with the Zen 3 microarchitecture. A new layout, significant architectural changes to the modules, and a more fine-tuned tech process that allows for 5GHz and sometimes even higher frequencies.

Everything the community asked for, the community finally got. But that wasn't all of the surprises.

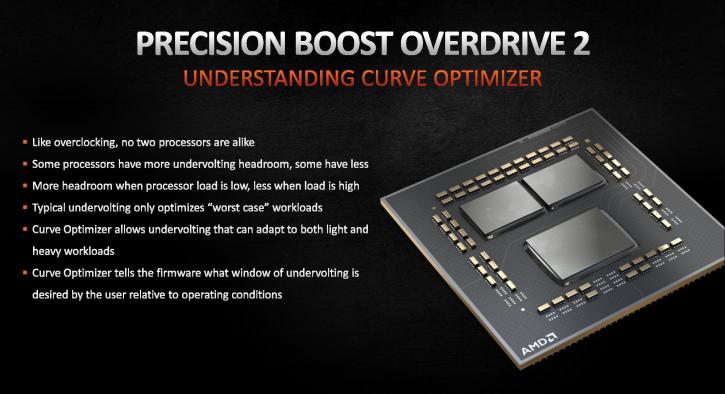

I think some of you remember the news that Ryzen processors with the Zen 3 microarchitecture were given the ability to customize frequencies for cores individually. At the time of the release, this turned out to be a slightly different feature than the news says - individual voltage control for the cores is referred to as "Curve Optimization."

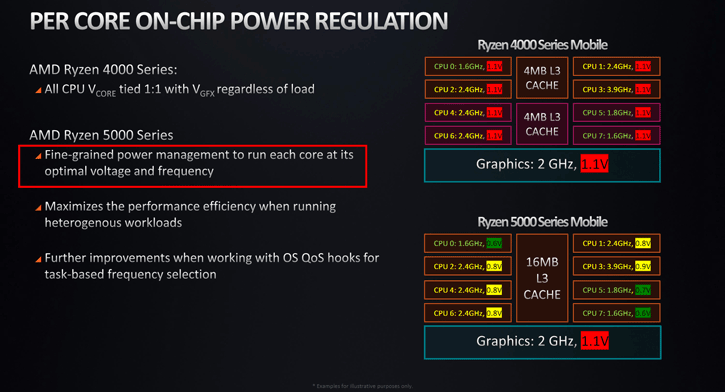

To my surprise, there was no mention of active dLDO in the presentation slides at all. During the development of CTR, it was discovered that during the boost to all cores, each core gets its own individual portion of voltage depending on the individual silicon characteristics (FIT). Information about this nice architectural feature started to flicker at the time of the Cezanne codename processors announcement, although it existed already in the Renoir codename processors.

Also, I can note that AMD managed to overcome weak single-core boost or single-core boost from cores that had mediocre silicon performance and fault tolerance. Now, the labeling of CPPC cores corresponded to reality, and SMU intelligently use cores with maximum energy efficiency in low threaded applications. At this second, it may seem to you that everything is optimized or overclocked to you, and we, enthusiasts, have nothing else to do here, but it's not so.

Nobody canceled the "strength" of silicon or, as some call it, "potential" because long testing of silicon in factory conditions is both additional time and additional resources, which may eventually lead to a disproportionate increase in the cost of the product. So, there is a template of testing silicon with certain tolerances (required range) for voltages relative to certain frequencies, which will be used to select the chips. Depending on that, they will get either Ryzen 7 5800X or Ryzen 9 5900X (for example). In the end, each processor has a chance of the lottery, but the processors with two CCDs have a greater chance of a performance boost. Here's an example. Ryzen 9 5900X and Ryzen 7 5800X processors have similar TDP and PPT, but have dramatically different performance. This suggests that the chips used in Ryzen 9 5900X have a better frequency to voltage ratio and such processors usually have a huge potential for overclocking. Ryzen 9 5950X processors, in turn, have the best ratio of frequency vs. temperature. Also, Ryzen 9 5900X and Ryzen 9 5950X processors have another interesting feature. CCD#1 is always a super binned specimen, and in most cases, it is the CCD capable of conquering the 5GHz mark. In contrast, CCD#2 is just an add-on with a medium binning category to reduce the cost of the final product, and often it is CCD#2 that we most often use as the main CCD in Ryzen 5 5600X.

As for the technological process, it has been significantly refined. Previously, for Zen 2, microarchitecture needed about 1.1V to conquer the frequency of 4050MHz, now for Zen 3, we can expect 4375MHz at 1.1V, which is +8%, while static leakage currents are almost unchanged. AMD also took care of eliminating temperature peaks previously observed in idle mode in a large proportion of processor owners with the Zen 2 microarchitecture. Voltage can now drop as low as 0.3V, and short-term background activity of operating system no longer triggers maximum performance state with VID value of 1.45V. Operating temperatures during load are unchanged, but high-performance cooling is also recommended as it affects boost and potential in CTR. A difference of around 300MHz when comparing normal air cooling and custom cooling.