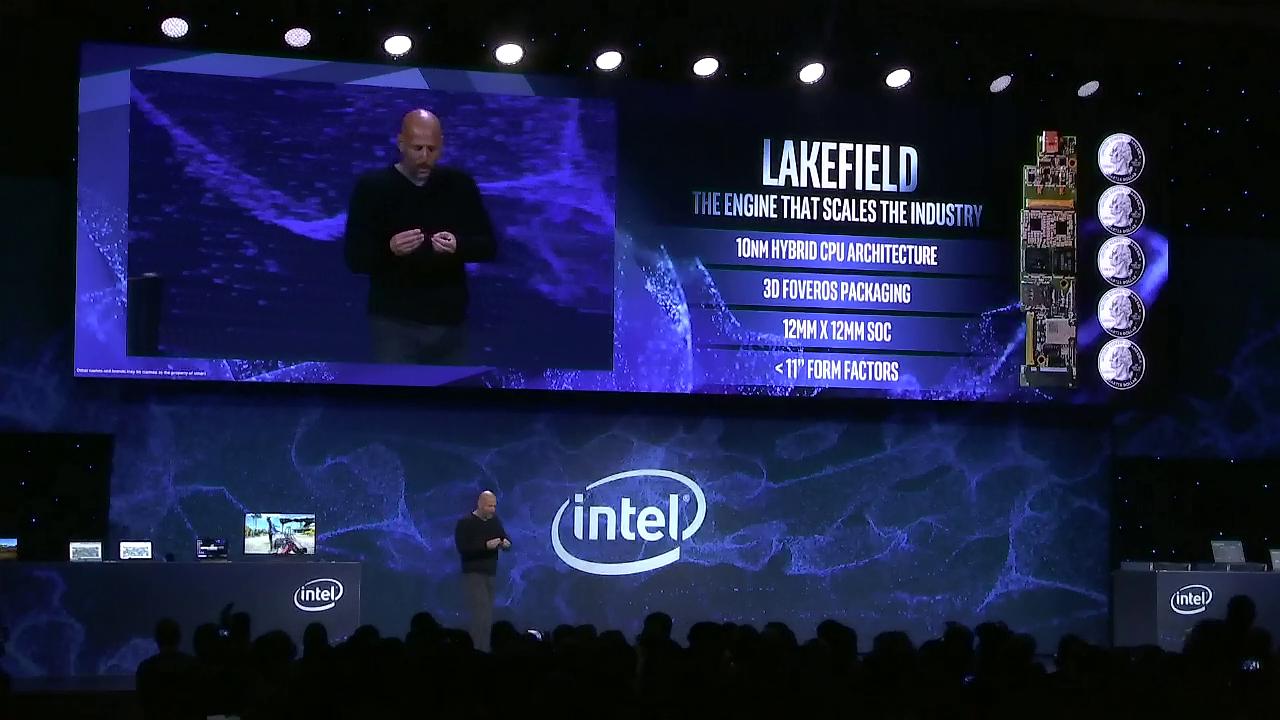

Intel has been talking about Lakefield, the processor will use different stacked CPU cores inside the package, making it a hybrid design based on Foveros technology. The processor only measures 12 by 12 mm and will get one main core and four atom cores combined with a chipset and LPDDR4X.

Intel presented the Lakefield chip at the CES 2019, it is intended for convertibles and uses a design of several vertically stacked dies in an effort to achieve performance with high efficiency in the smallest possible space. Lakefield in idle only would use 2 milliwatts.

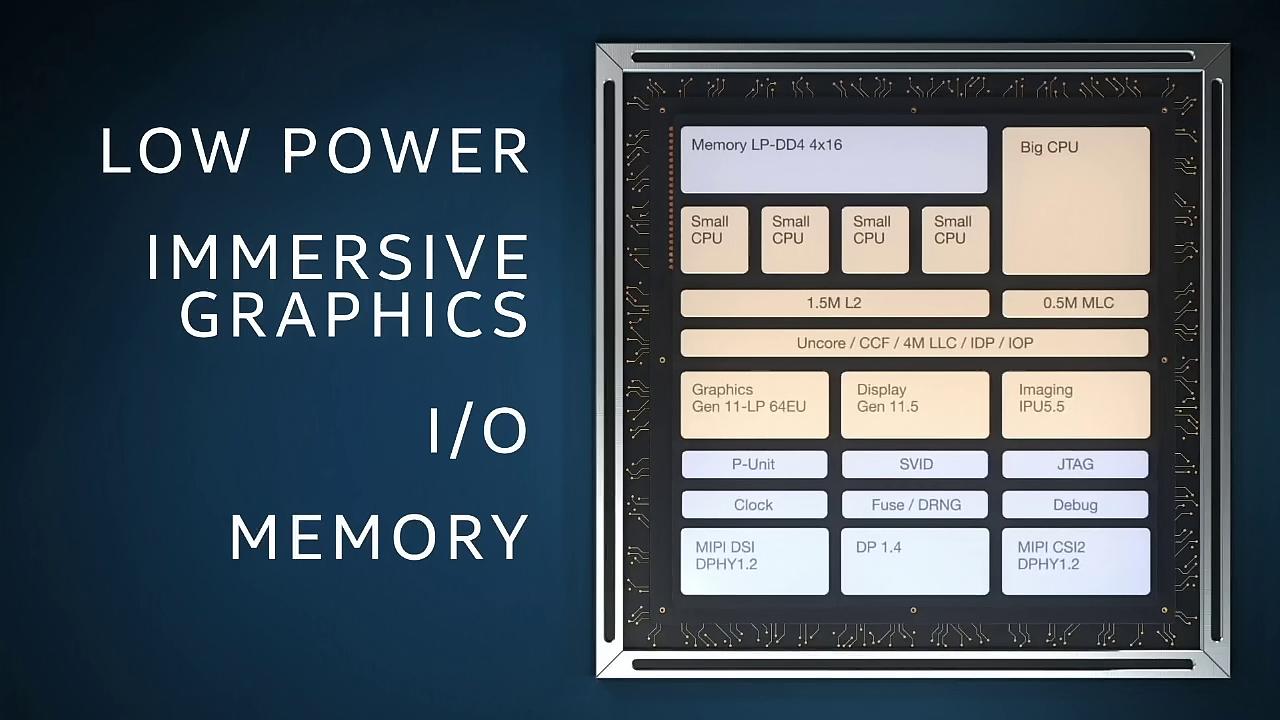

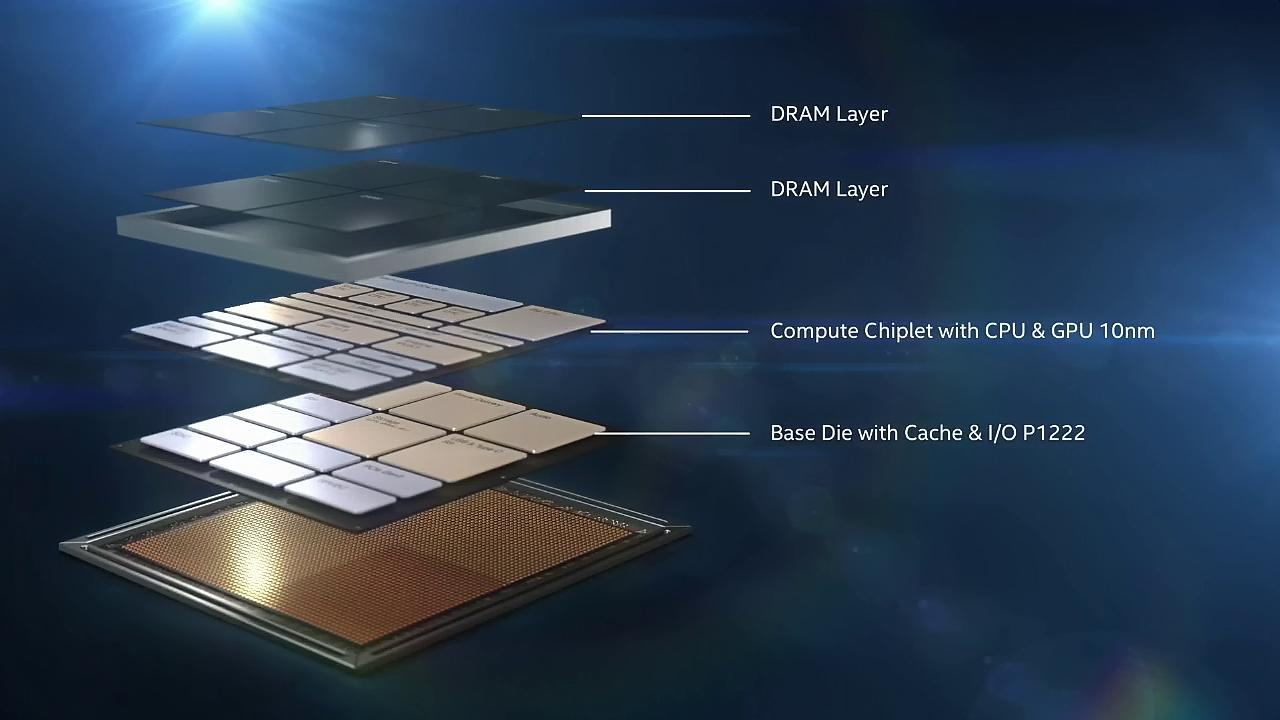

The design consists of three parts and is strongly reminiscent of those used in smartphones, with one big difference: instead of putting memory on a die, Intel pairs two all managed by the so-called 3D Foveros packaging technology, which basically is 3D stacking to connect multiple chiplets. Intel uses an interposer, which is produced in a 22FFL process and contains I/O functions such as SATA or USB. On top of that, through-contacted (TSV) there will be a 10nm based compute die as well as the RAM controller with a 64-bit interface, and at the top then the LPDDR4X main memory as a classic PoP (Package on Package). Intel previously strictly differentiated between core and Atom processors, the Compute-Die combines these two types of x86 CPU cores; a bit like ARM's big-LITTLE methodology. A Sunny Cove core, that's the name of the architecture of the upcoming Ice Lake chips, is expected next to four Tremont cores (next-gen Atom cores). The five cores will share 4 MB of L3 cache and are tied to a Gen11 GT2 integrated graphics unit with 64 execution units.