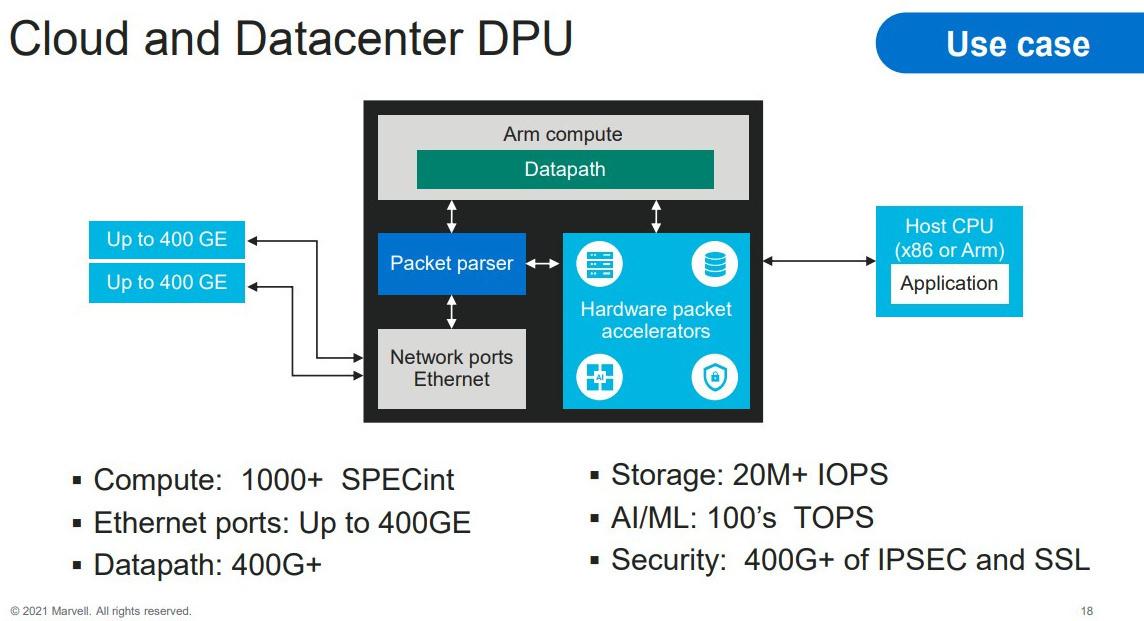

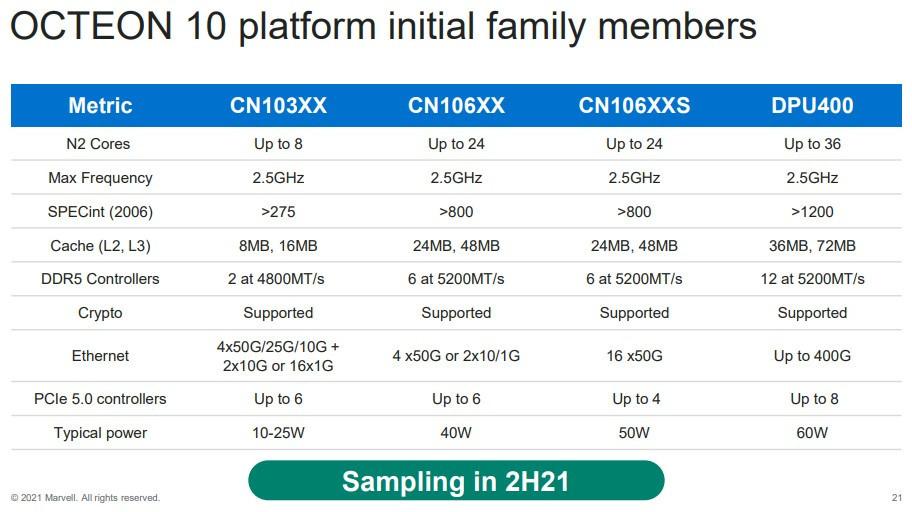

The network chip Octeon 10 has been announced by Marvell. Aimed at the server market and fabulated at 5nm node of TSMC, it contains up to 36 Arm Neoverse N2 CPU core, which is supported with ECC and is equipped with six-channel ddr5-5200.

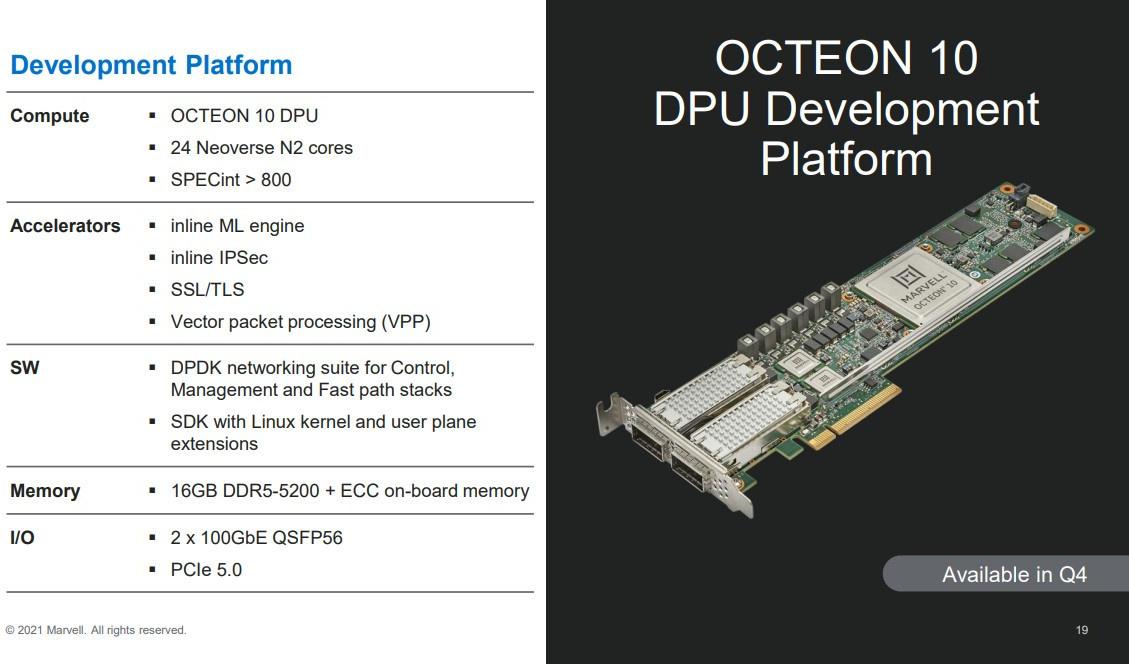

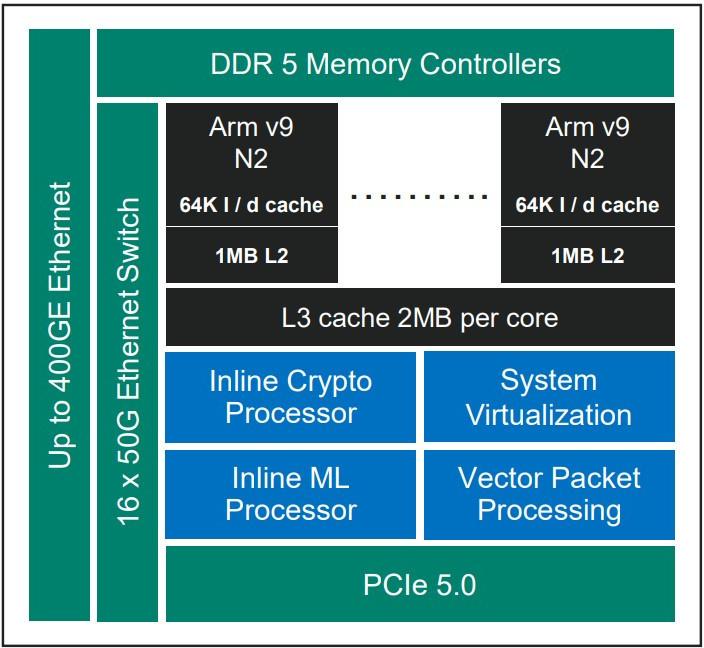

The Neoverse N2 cores have the largest cache configuration, which means that they contain 64 KB L1 cache and 1 MB L2 cache per core. The shared L3 cache has sizes from 8 MB to 72 MB. The integrated Ethernet switch supports 16 channels of 50 gigabits each, and there is also a configuration that allows speeds of up to 400 gigabits. It features a PCIe 5.0 x8 connector. The entry-level chips bear the CN103XX hallmark and offer up to eight N2 cores. They consume 10 to 25 watts and therefore have support for four 50Gbit ports. The tdp of the DPU400 top model increases to 60 watts. That is considerably less than the current Octeon TX2 flagship, which consumes 80 to 120 watts (depending on the configuration).

“To meet and exceed the growing data processing requirements for network, storage, and security workloads, Marvell focused on significant DPU innovations across compute, hardware accelerators, and high speed I/O,” said John Sakamoto, vice president of Marvell’s Infrastructure Processors Business Unit. “The OCTEON 10 brings compute leadership, supports networking and security workloads exceeding 400G, and incorporates leading edge I/O including DDR5 and PCIe 5.0.”

In SpecInt2006, the CPU in the base model reaches at least 275 points, the DPU400 top model exceeds 1200 points. Marvell emphasizes that this benchmark is still used to provide an accurate picture of what previous generations offer. The tape-out phase has already had the network chip, and the sampling phase is expected to start in the second half of this year.

Marvell Unveils Octeon 10 Network Adapter with 5nm DPU, DDR5 and PCIe 5.0