OCTEON TX2 is processors are targeting a wide variety of wired and wireless networking equipment including switches, routers, secure gateways, firewall, network monitoring, 5G base stations, and smart network interface controllers (NICs).

Massive increases in data traffic coupled with escalating requirements for end-to-end security are intensifying the need for highly scalable compute platforms with integrated workload-optimized hardware accelerators to meet performance, power and total cost of ownership requirements. Building on five generations of the industry's most scalable and widely adopted infrastructure processor platform, the OCTEON TX2 family is enabled by a broad software ecosystem including a feature-rich software development kit (SDK) and virtualization support, delivering a unique combination of performance and programmability. The OCTEON TX2 portfolio extends Marvell's industry-leading performance and scalability, delivering a 2.5x improvement over the previous generation and scaling up to 200 Gbps of packet processing throughput.

Marvell's OCTEON TX2 infrastructure processor family combines up to 36 cores, based on the Arm v8-A architecture with configurable and programmable hardware accelerator blocks, connected by Marvell's field-proven and highly scalable coherent interconnect. Compared to architectures that process data solely on CPU cores, these accelerator blocks - which include security, packet processing, and traffic management functions - are able to meet the most demanding performance and power requirements. The integrated hardware accelerators offer 2.5x improvement over Marvell's previous generation of OCTEON processors with scalable throughput ranging from 10 Gbps to over 200 Gbps making them ideal for 5G base station and transport network infrastructure, security, cloud and data center, enterprise networking, and intelligent offload applications.

The OCTEON platform is enabled by a mature and widely deployed SDK, supported by robust software ecosystems consisting of both open source and commercial offerings. The platform includes firmware, Linux OS and multiple distributions, virtualization, containers, data plane development kit (DPDK), protocol stacks, infrastructure management and orchestration like OpenStack and Kubernetes, and virtual network functions (VNFs). In addition, Marvell supports a full routing stack including TCP, SSL, and IPSEC support and DPDK support for L2/L3 forwarding and IPSEC.

"Today's data infrastructure requires significantly faster network throughput and higher end-to-end security at all nodes of the network," said John Sakamoto, vice president of Infrastructure Processor Business Unit at Marvell. "Built on more than a decade of expertise, the OCTEON TX2 family extends Marvell's performance leadership in supporting high performance datapath and security applications with a 2.5x performance boost over previous generations."

"High-performance data networks require increased compute performance and efficiency as we enter the 5G era," said Mohamed Awad, vice president of marketing, Infrastructure Line of Business, Arm. "OCTEON TX2, based on the Armv8-A architecture, enables new levels of performance to meet the demands of next generation networking and cloud data center applications."Marvell's CN91xx, CN92xx, CN96xx, and CN98xx processor families include:

- 4 - 36 cores based on the Armv8-A architecture ranging up to 2.4 GHz frequency

- Rich I/O with 25G SerDes-based I/O interfaces, e.g. 100GbE, 50GbE, 40GbE, 25GbE, 10GbE, 2.5GbE, 1GbE Ethernet ports and PCIe gen4 interfaces supporting root-complex and end-point configurations

- Enhanced NITROX V security co-processors which accelerate a comprehensive set of asymmetric and symmetric cryptographic operations

- Hardware accelerators support with comprehensive packet processing hardware offload, including packet receive, flexible packet parsing, flow classification, buffer management, QoS (quality of service), transmit processing and hierarchical traffic shaping and scheduling

- Innovative and unique load-balancing and work scheduling hardware which accounts for QoS, packet ordering and synchronization

Marvell's OCTEON TX2 CN9130, CN92xx and CN96xx are available now with reference designs and development kits. Marvell's CN98xx will begin sampling in the second quarter of 2020.

Feature Table

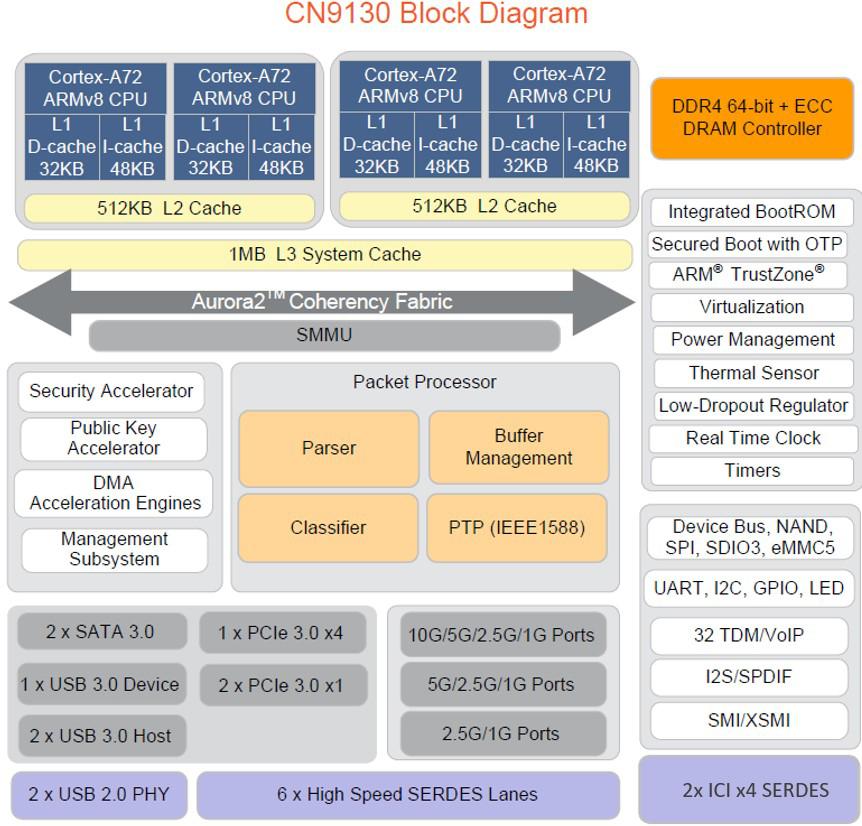

| FEATURES | OCTEON TX2 CN9130 | OCTEON TX2 CN9131 | OCTEON TX2 CN9132 |

|---|---|---|---|

| CPU | Quad Core Armv8 Cortex-A72, CPU frequency up to 2200 MHz | ||

| L1 Cache | 48 KB I-cache, 32 KB D-cache | ||

| L2 Cache | 1 MB total divided into two clusters of 512 KB ECC shared cache | ||

| L3 Cache | 1 MB with ECC | ||

| DDR4 | 64-bits + ECC at 1200Mhz clock | ||

| PCIe 3.0 | 1 Port x4 + 2 Ports x 1 Total of 3 controllers and up to 6 lanes |

1 Port x4 + 1 Ports x2 + 4 Ports x1 Total of 6 controllers and up to 10 lanes |

1 Port x4 + 2 Ports x2 + 4 Ports x1 Total of 9 controllers and up to 14 lanes |

| Ethernet Ports | 1x 10/5 GbE port + 2x 1/2.5 GbE Ports or 2x 5 GbE Port + 1x 1/2.5 GbE Port |

2x 10/5 GbE port + 4x 1/2.5 GbE Ports or 4x 5 GbE Port + 2x 1/2.5 GbE Port |

3x 10/5 GbE port + 6x 1/2.5 GbE Ports or 6x 5 GbE Port + 3x 1/2.5 GbE Port |

| USB 3.0 | 2 x USB 3.0 (Host/Device) |

4 x USB 3.0 (Host/Device) |

6 x USB 3.0 (Host/Device) |

| SATA 3.0 | 2 x SATA 3.0 | 4 x SATA 3.0 | 6 x SATA 3.0 |

| SERDES Lanes | 6 Lanes | 12 Lanes | 18 Lanes |

| CN9130 | CN9130 - HFCBGA 24x24 mm, 0.8 mm pitch | ||

| 88F8215 | 88F8215 – TFBGA 12x12 mm 0.5 mm pitch |

2x 88F8215 – TFBGA 12x12 mm 0.5 mm pitch |

|