The AMD Navi 4C GPU, previously anticipated to be part of the RX 8000 GPU series, has reportedly been cancelled. A recent Moore’s Law is Dead diagram revealed the Navi 4C design within the RX 8000 GPU series.

Initial indications pointed to the Navi 4C design being a part of the RX 8000 GPU series. However, developments suggest discontinuation of the Navi 41 and Navi 42 models that were initially planned. This cancellation is paralleled by AMD's approach towards further disaggregation of the GPU's features. Both the media acceleration engine and the Radiance Display Engine, previously integrated into the GPU architecture, are now being considered for separate inclusion. The media acceleration engine, although comprised of logic components, functions as fixed function hardware, akin to the display engines. These engines potentially retain operability on older foundry nodes. To realize this separation, AMD envisions a dedicated chiplet, termed MID (media and I/O die), to house the media acceleration and display engine. While the specific foundry node for the MID is yet undecided, AMD's successful integration of media and display I/O features onto the 6 nm Navi 33 silicon implies a potential employment of the older node.

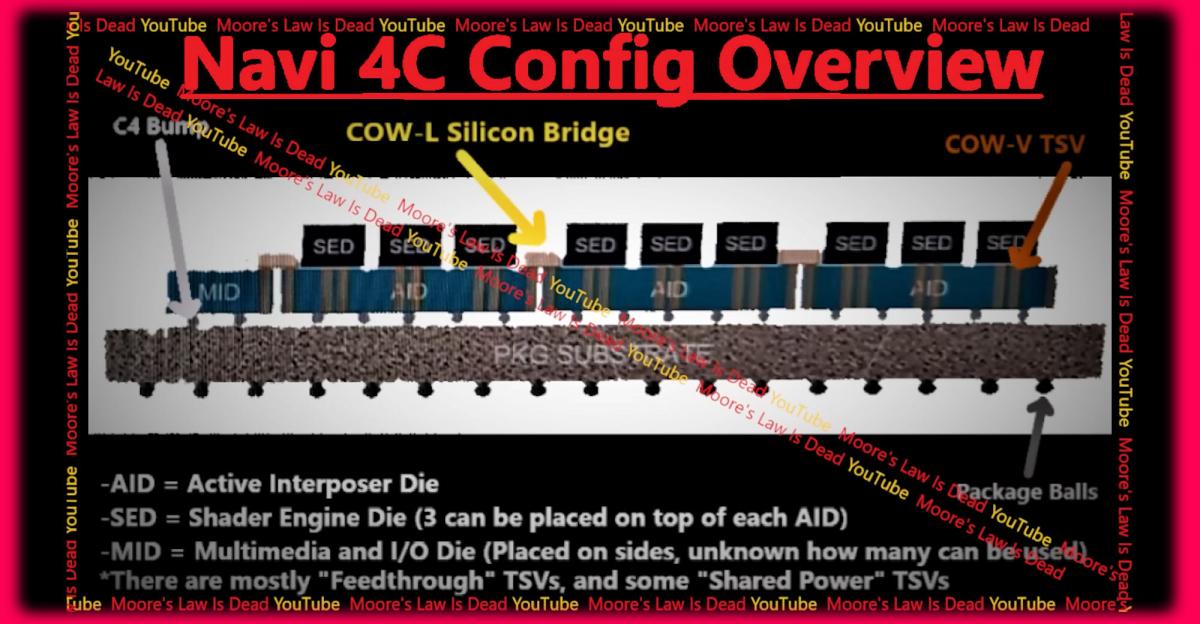

Another significant aspect of the architecture pertains to the Shader Engines, which AMD intends to segment into chiplets referred to as SEDs (shader engine dies). Each SED, housing a defined number of workgroup processors (WGPs), is likely to be produced on an advanced foundry node, potentially aligning with NVIDIA's exploration of the 3 nm Blackwell GPUs. These SEDs are integrated within active interposer dies (AIDs), facilitating high-density microscopic wiring between chiplets. The term "active" in AID signifies not just the wiring among stacked dies but also interconnections between neighboring AIDs. TSMC's development of the COW-L (chip-on-wafer-L) bridges facilitates this inter-AID high-density wiring. The specifics of their interface with the MCDs (memory controller dies) remain speculative. The diagram offered in the disclosed information depicts a package substrate accommodating three AIDs and one MID. Each AID appears capable of accommodating up to three SEDs, suggesting a potential architecture for the RDNA4 design or a segment thereof. However, it's crucial to note that this diagram offers only a partial representation of the entire design.

The complexity of the proposed Navi 4C GPU is underlined by Moore’s Law is Dead. The patent "Die stacking for modular parallel processors" illustrates a design resembling the Navi 4C's package layout. This concept was introduced by Kepler_L2, referencing not just Navi 4C but also Navi 4X and Navi 4M models, although specifics about these models remain undisclosed. The association between C/M/X designations and Navi 41/42 is yet to be clarified, showcasing the intricacy of AMD's Navi 4 project.

Analyzing the Unreleased AMD Navi 4C GPU