You know it for them recent Intel rumours, processors with a couple of energy-friendly cores, and then some huge ones for heavy-duty processing. It seems to be something that AMD wants to explore as well, as they filed a patent for it.

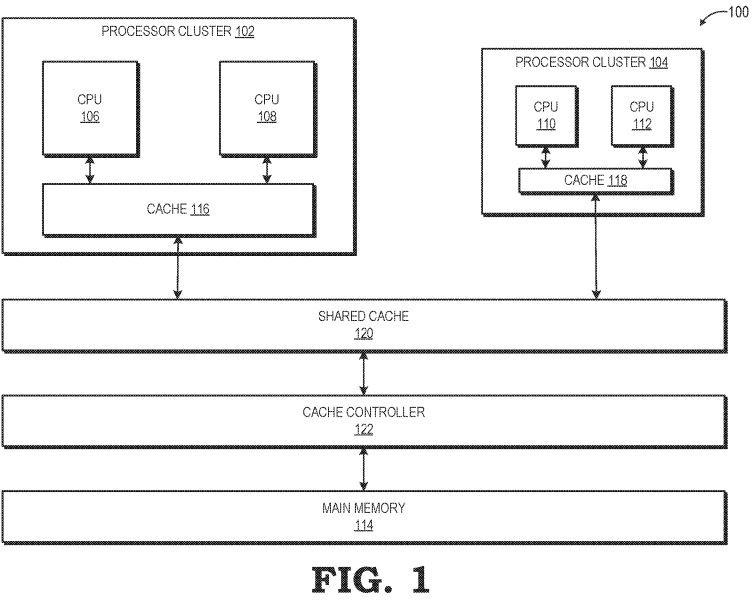

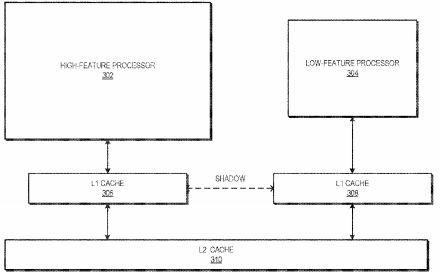

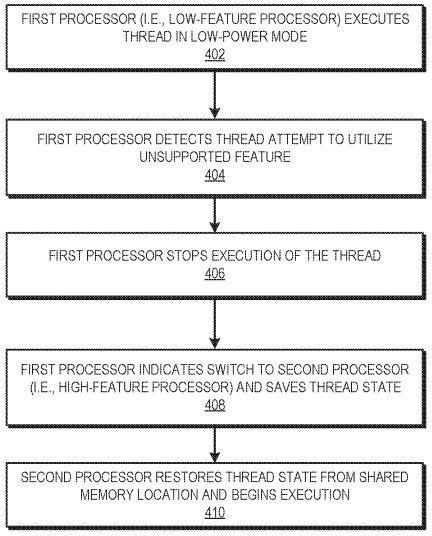

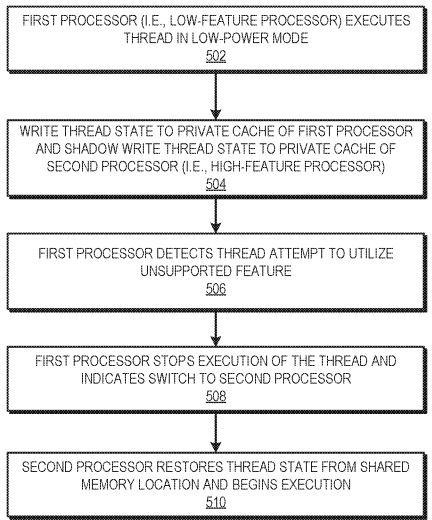

Much like Intel Lakefield, the small cores deal with light tasks more energy-efficiently, while the large cores are better suited for the heavy work. The patent shows a schematic of a theoretical chip with two groups of cores. Both the large and small cores have their own cache, the next cache level share the two types of cores. The design here is interesting as for some usage the operating system is not needed into the mix, the processor itself could make decisions on what to run where. Also, these do not necessarily need to be CPU cores, GPU cores can also be used as well. That makes this complicated but usability, extremely large.

The patent request appears to be still in an early phase, information and designs thus can change. Also, it's a patent, so it's not a sure thing hat a design likely this will ever see make it into the real world. But interesting it is, as AMD is eying that big LITTLE concept.

AMD Flirting with big.LITTLE processor design - files a Patent