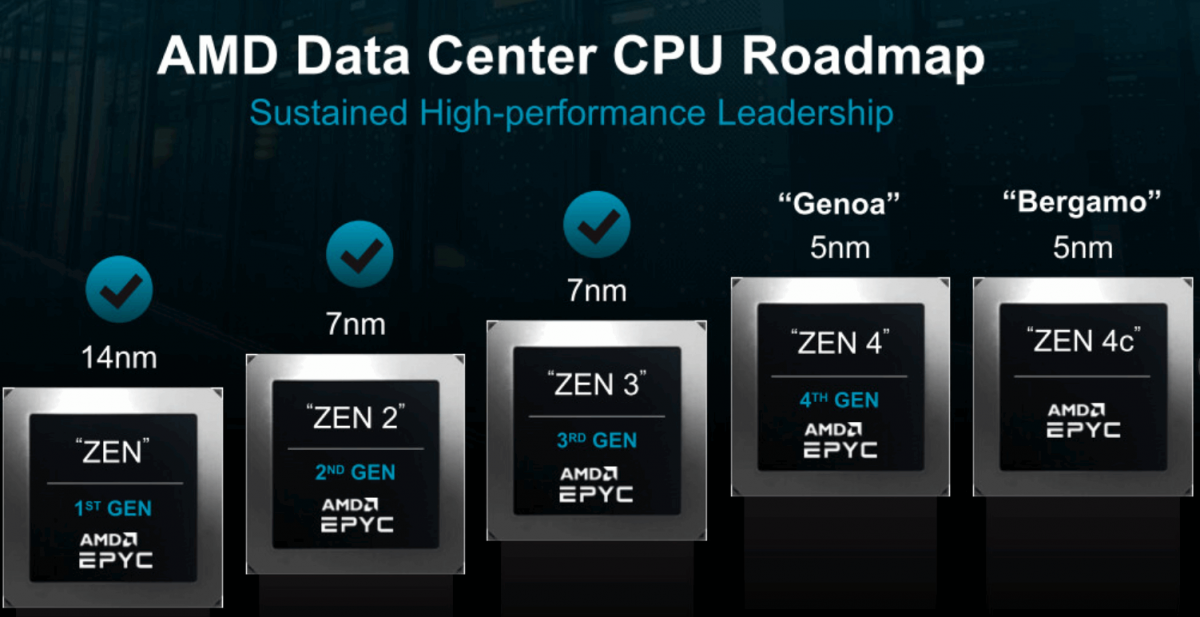

The AMD EPYC 'Bergamo' is a cloud-optimized CPU with Zen 4c microarchitecture and exhibits a core size reduction of 50% compared to its Zen 4 predecessor. The EPYC 'Bergamo' comprises 128 cores and aligns with the Socket SP5, the same as the 96-core EPYC 'Genoa'.

The processor incorporates a 12-channel DDR5-4800 memory subsystem and incorporates the 'Floyd' I/O die, supplying 128 PCIe Gen5 lanes along with other SP5 specific traits. As a cloud-native system-on-chip (SoC), Bergamo is developed with a focus on operational efficiency, power consumption, die size, and comprehensive total cost of ownership (TCO), instead of prioritizing per-core performance exclusively. This strategic approach is in response to the rise of Arm-based datacenter-grade SoCs by firms such as Ampere, Amazon, Google, and Microsoft.

The Zen 4c microarchitecture preserves the Zen 4 design elements and instructions-per-clock efficiency, but employs a distinctive implementation strategy. SemiAnalysis reports that the Zen 4c 'Dionysus' cores are around 35.4% smaller than Zen 4 'Persephone' cores. To accomplish this reduction, AMD incorporated several design modifications:

Further methods were applied to decrease die area. The Bergamo SoC incorporates eight Vindhya core complex dies (CCDs), each housing 16 Zen 4c cores (double the Zen 4 cores per CCD). Each CCD consists of two eight-core core complexes (CCX) with 32MB of L3 cache, allocating 16MB per CCX. In contrast, a Zen 4 CCX has 32MB of L2 cache, which is larger than the Zen 4c CCX.

AMD is expected to introduce two Bergamo processors this month: the 128-core EPYC 9754 and a slightly modified 112-core EPYC 9734. Keeping in mind the distinctive needs of exascale datacenter operators, AMD will likely develop tailored and semi-custom Bergamo models in the future. However, the immediate focus is on the launch of these two models next week.

AMD's EPYC Bergamo: Cloud-Native CPU Based on Zen 4c Architecture