Way ahead of schedule (the target was late Summer) Micron has started shipping GDDR5X Memory its customers, likely Nvidia first. Micron will offer the ICs in 8 Gb (1 GB) and 16 Gb (2 GB) densities which indeed is indicative for 8GB adn 16GB graphics cards. The upcoming GeForce GTX 1070 and 1080 (if they are named that) already have been indicated as 8GB products.

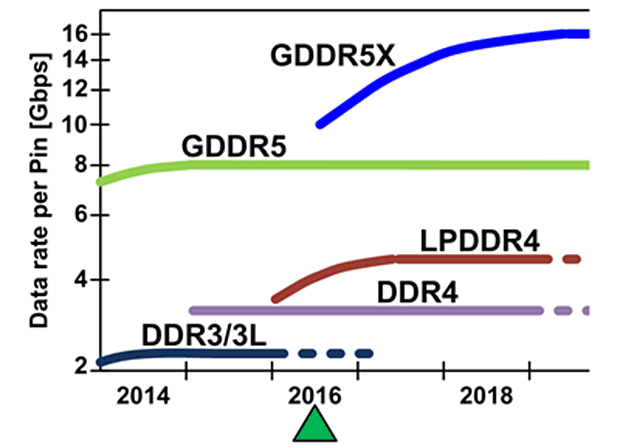

GDDR5X is your standard GDDR5 memory however, opposed to delivering 32 byte/access to the memory cells, this is doubled up towards 64 byte/access. And that in theory could double up graphics card memory bandwidth. Early indications according to the presentation show numbers with the memory capable of doing up-to 10 to 12 Gbps, and in the future 16 Gbps. So your high-end graphics cardsthese days hover at say 400 GB/s. With GDDR5X that could increase to 800~1000 GB/sec and thus these are very significant improvements, actually they are competitive enough with HBM.

The big advantage of 64 byte/access GDDR5X is that it doesn't need hefty design changes other it would need compatible memory controllers, so this might be a very cost efficient methodology until HBM has matured and will be a more affordable solution.

AMD and NVIDIA are working on GDDR5X support.

Told ya ;)

Micron Starts Sampling GDDR5X Memory to Customers