Another day, another leak. This round information on Intel leaked like melting ice cream, yep Ice Lake in specific, well actually Tiger Lake, but that's more or less the same. If you can remember it, that's the dreaded 10nm node that is causing so many issues. Intel is continuing though, on the ultra-thin and ultra-low-power designs.

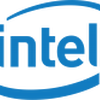

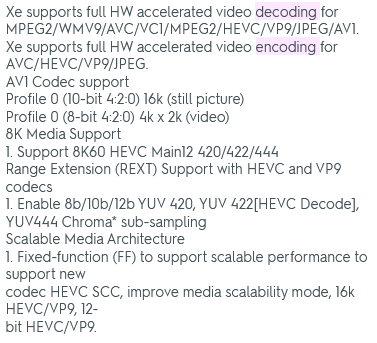

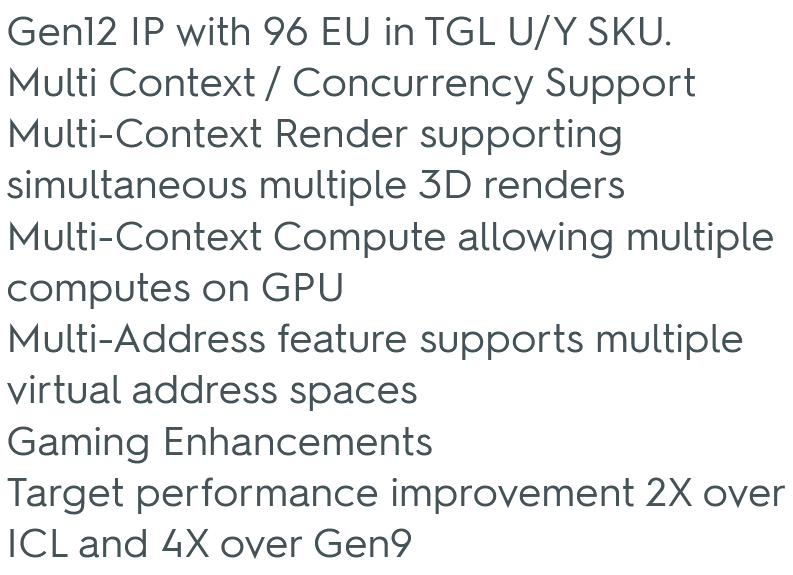

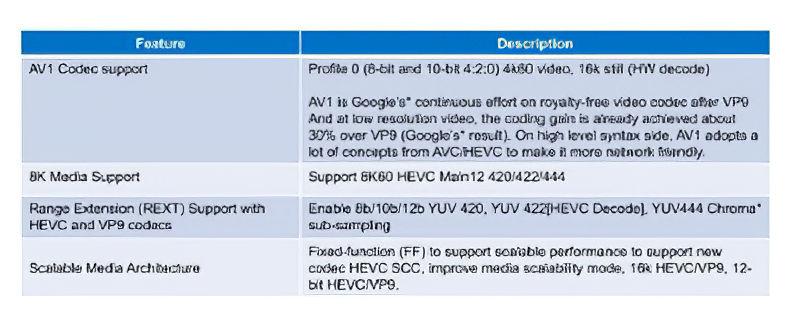

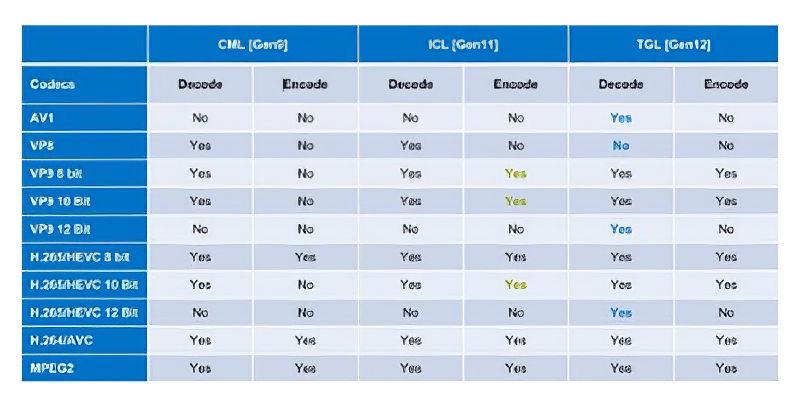

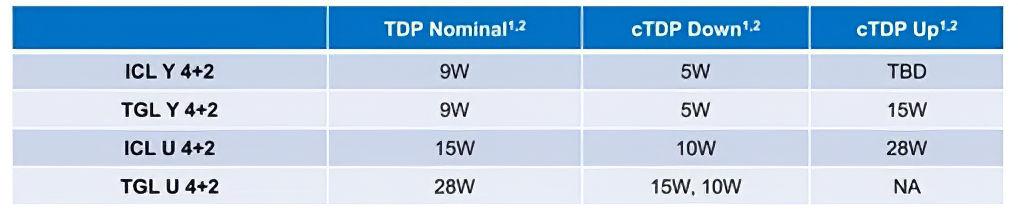

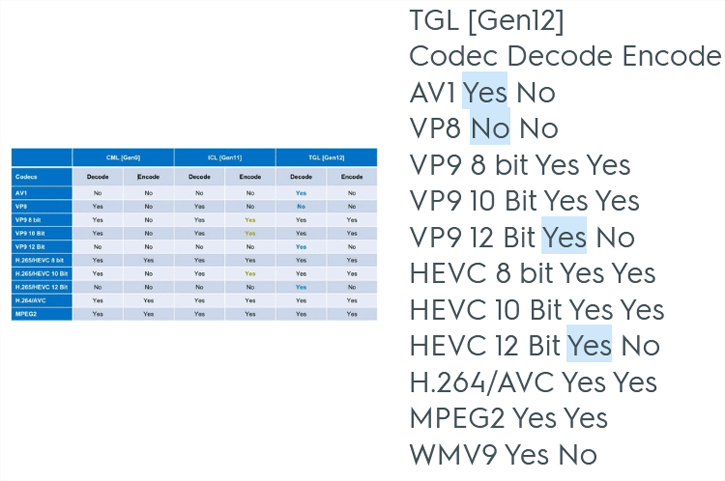

So first things first, Tiger Lake is an Intel CPU microarchitecture based on the third-generation 10nm process node (named "10nm++"). It will replace Ice Lake, representing the Optimization step in Intel's Process-Architecture-Optimization model. In specifically that segment you can expect Tiger Lake processors, SoC's we should say up-to four cores with TDPs ranging from 9 running to 28 Watt. Tiger Lake is going to be a 4+2 design, and that means 4-cores and 2 Gen12 iGPU clusters. Tiger Lake would feature up to 768 Shading Units. BTW the slides confirm VP1 decoding support.

In the ultra-thin and ultra-low-power it could take on 4-core Renois parts, AMD's upcoming Ryzen 4000 APUs based on ZEN2.

| Intel Tiger Lake | Intel Ice Lake | AMD Renoir | |

|---|---|---|---|

| Die Size | 146 mm2 | 122 mm2 | 156 mm2 |

| Core Design | Willow Cove | Sunny Cove | Zen2 |

| Node | 10nm | 10nm | 7nm |

| CPU | 2 / 4 | 2 / 4 | 4 / 6 / 8 |

| GPU Shaders | 384 / 512 / 640 / 768 | 256 / 384 / 512 | 384 / 448 / 512 |

| GPU Architecture | Gen12 (Xe) | Gen11 | GCN 5.0 (Vega) |

| PCIe Gen | 4.0 | 3.0 | 4.0 |

| Thunderbolt Gen | 4.0 | 3.0 | 3.0 |

| TDP | U (28/15W) / Y (9W) | U (28/15W) / Y (9W) | U (15W), H (45/35W), G (65W) |

Intel Tiger Lake (Xe) Graphics Details Slide Leaks