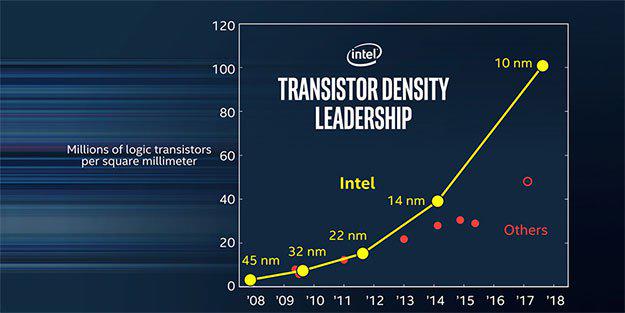

Intel is pushing hard with the production of 10nm processors, the chip yield is currently low, Intel delivers only a few CPUs to partners. Ice Lake is expected to appear in 2019.

The 10-nm series production is scheduled to start at Intel in the second half of 2018, which has announced CEO Brian Krzanich in discussing the results of the fourth quarter of 2017 mentions Golem. According to Krzanich, in the coming months, the chip yield (yield) will be increased dramatically for proper mass production, the manufacturer so far has sent only limited samples of Cannon Lake U to close partners.

Apparently, the plan is to switch from 10 nm to 10+ nm as quickly as possible, a slightly improved version of the fabrication node. Ice Lake is to be created with this production technology. Intel intends to use these processors in all segments from the tablet to up-to supercomputer.

For Ultrabooks, Intel is planning a follow-up to Whiskey Lake for Kaby Lake Refresh , another 15-watt quad-core. In addition to a 4 + 2 design with four cores and GT2 graphics unit is also one with 4 + 3 planned, but then called Coffee Lake U. This design uses a GT3, the more shader cores and also EDRAM as a fast On -Package memory uses. Whiskey Lake U and Coffee Lake U are apparently manufactured at 14++ nm.

For a higher class of performance, the Coffee Lake H are planned, which are Hexacore chips with 45 watts of thermal loss. They follow Kaby Lake H with four cores and are said to clock very high at up to 4.8 GHz . Top model will probably be the Core i9-8950HK with open multiplier for notebook overclockers. Thus far Intel uses the Core i9 designation only for desktop chips like the Core i9-7980XE with 18 CPU cores.

Intel Likely Starts 10nm Volume Production in the second half of 2018