Intel has unveiled a pioneering manufacturing technique known as PowerVia, which deviates from traditional practices by supplying power from the rear of the wafer instead of via the transistors.

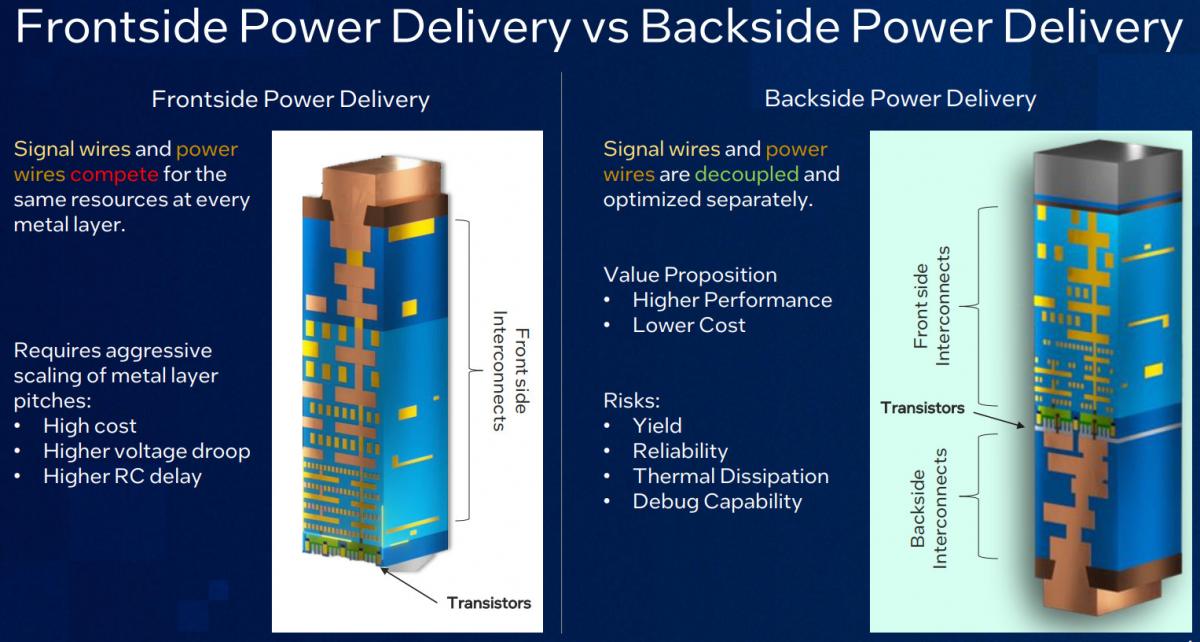

This avant-garde approach streamlines the design process and optimizes expenses. Upon the chip's completion, it is flipped over, enveloped in a packaging that facilitates external connectivity, and is then prepared for computer integration. Regrettably, this method is encountering challenges. With increasing miniaturization and density, the layers sharing interconnects and power connections have transformed into a progressively disordered network, negatively affecting each chip's overall performance. Previously overlooked, "these connections now wield substantial influence," according to Ben Sell, Intel's vice president of Technology Development and a member of the PowerVia development team. In essence, power and signals tend to deteriorate, necessitating workarounds or an influx of additional power.

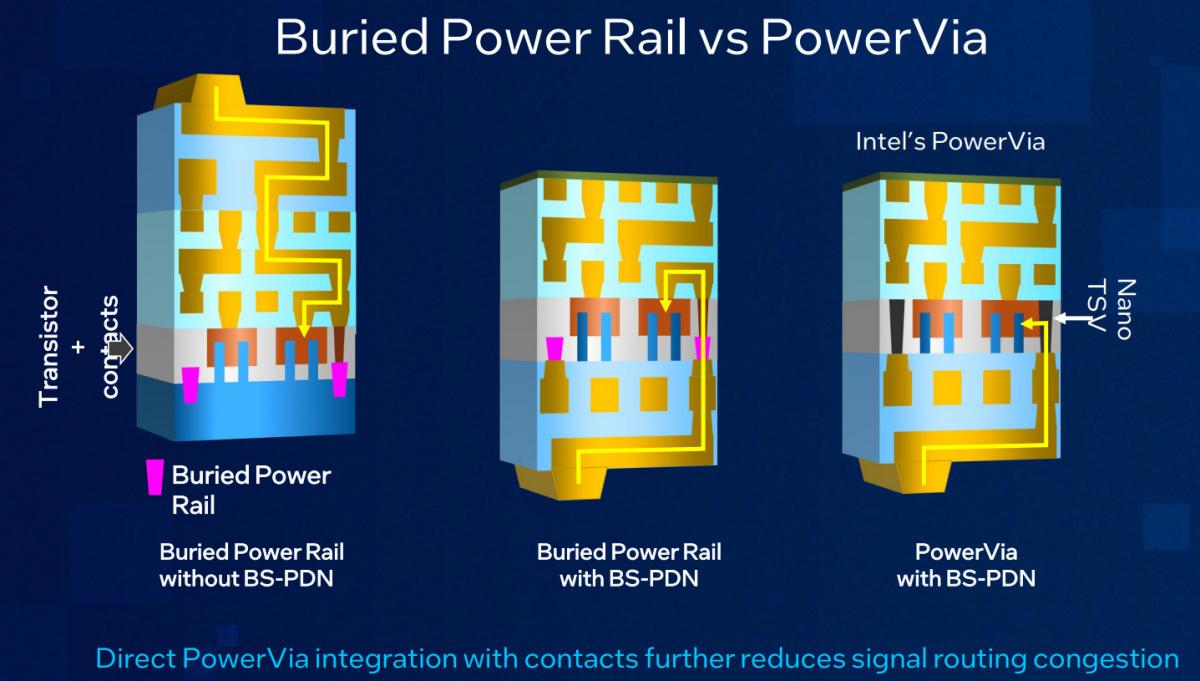

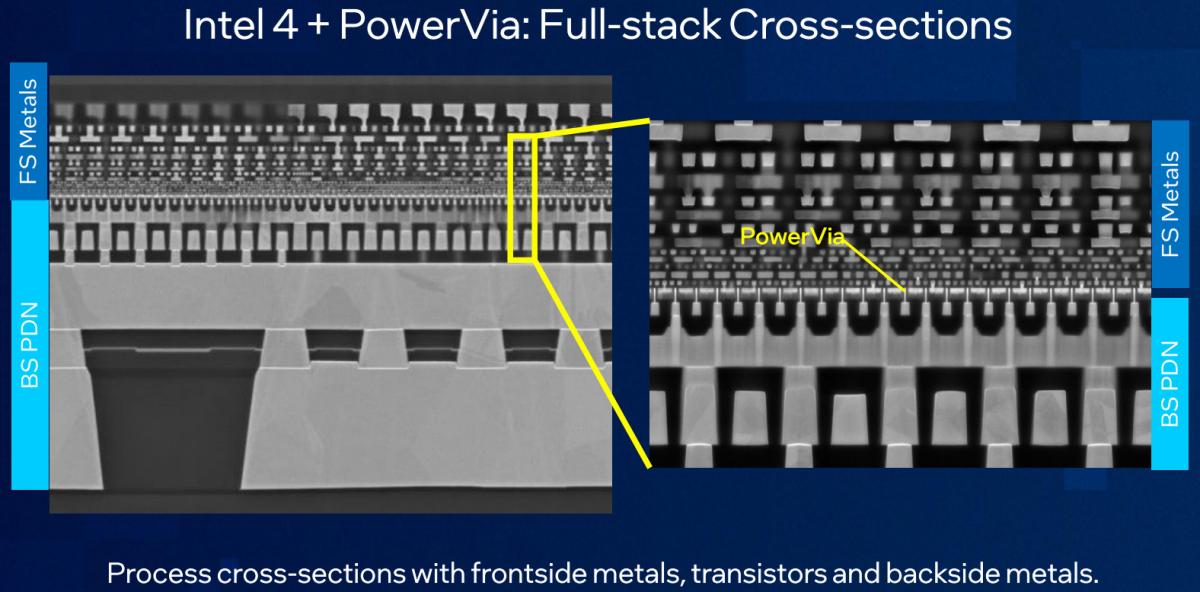

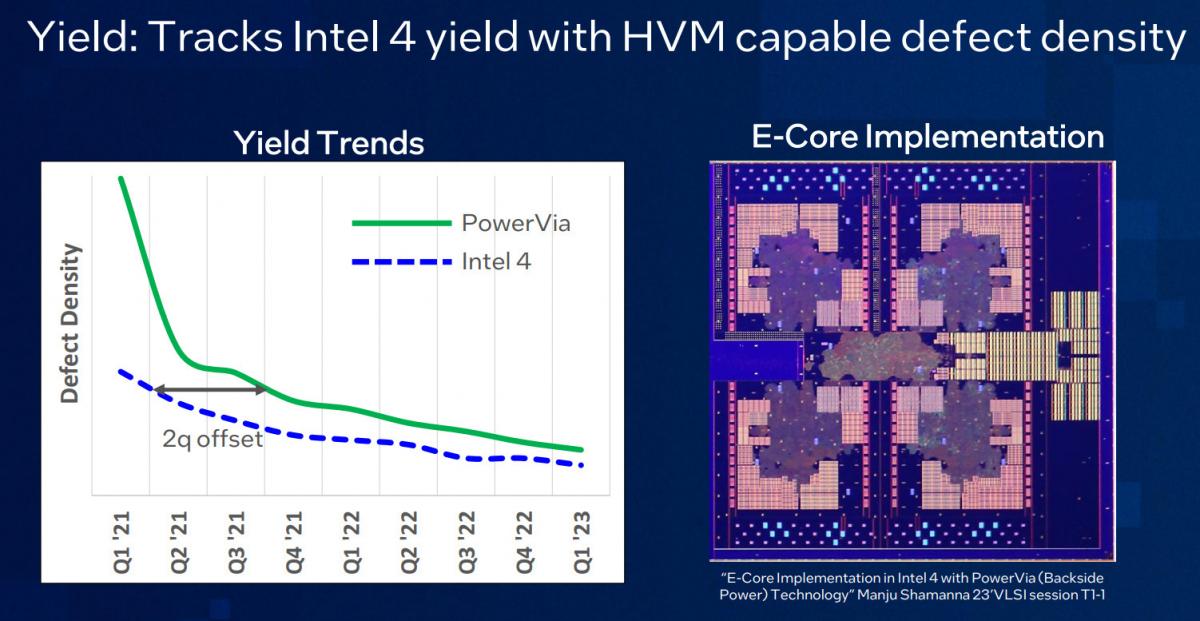

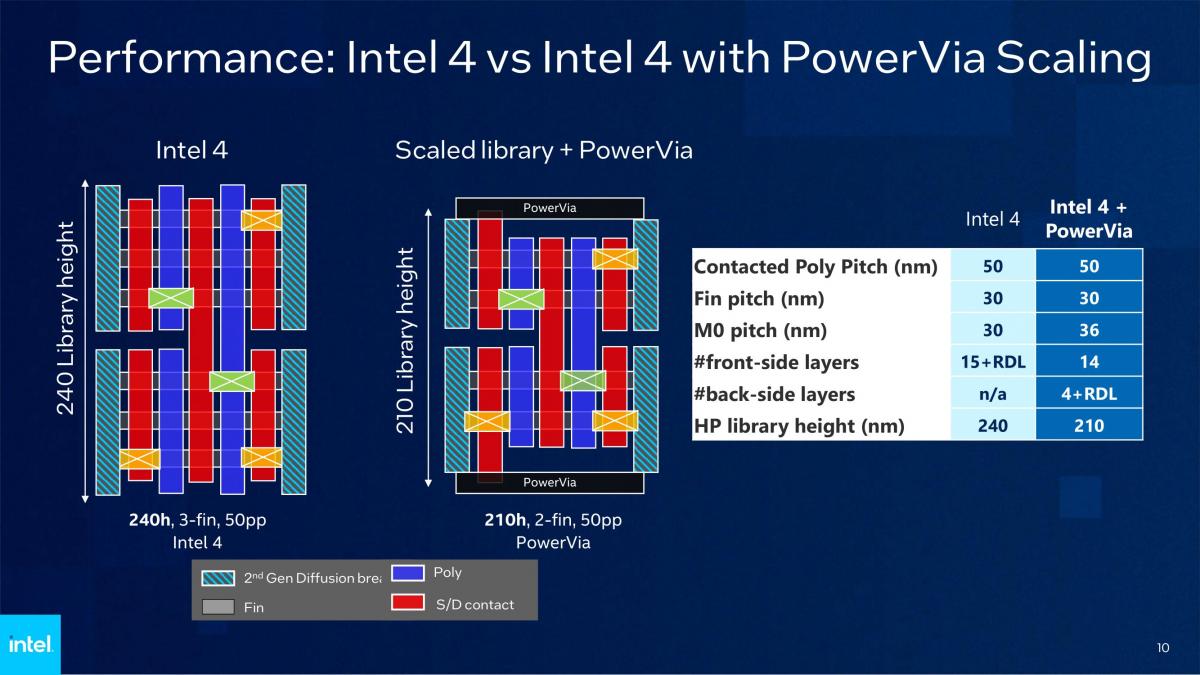

In addition, PowerVia may potentially mitigate power droop and incrementally augment processing speed. This technology was successfully implemented on a trial processor that utilizes the Intel 4 architecture and incorporates four Crestmont e-cores, with plans for future deployment in Meteor Lake. The decision to test PowerVia with the preceding 7nm process ensured an uninterrupted development trajectory for the 20A and 18A nodes. Notably, this power delivery method will make its first appearance in products crafted using Intel's maiden Angstrom processes. Mass production of the 20A node, which amalgamates RibbonFET and PowerVia, is estimated to commence in the first half of 2024. This evolution anticipates numerous advantages, such as reducing the interference between power and data signals and facilitating separate optimization processes. The results also include a 30% reduction in IR voltage droop at the package level and a 6% enhancement in clock speed. The chip production process is further rendered more economically feasible. Power is transferred via ultra-thin nano through silicon vias, signalling a significant advancement over current methods. Intel has also surmounted potential PowerVia-related hurdles, including heat dissipation management and the evolution of debugging techniques, which are typically executed from the bottom.

Intel Introduces Breakthrough Power Delivery Technique for Next-Generation Processors - PowerVia

.jpg)