A group of leading technology companies today announced the Gen-Z Consortium, an industry alliance working to create and commercialize a new scalable computing interconnect and protocol.

This flexible, high-performance memory semantic fabric provides a peer-to-peer interconnect that easily accesses large volumes of data while lowering costs and avoiding today's bottlenecks. The alliance members include AMD, ARM, Cavium Inc., Cray, Dell EMC, Hewlett Packard Enterprise (HPE), Huawei, IBM, IDT, Lenovo, Mellanox Technologies, Micron, Microsemi, Red Hat, Samsung, Seagate, SK hynix, Western Digital Corporation, and Xilinx.

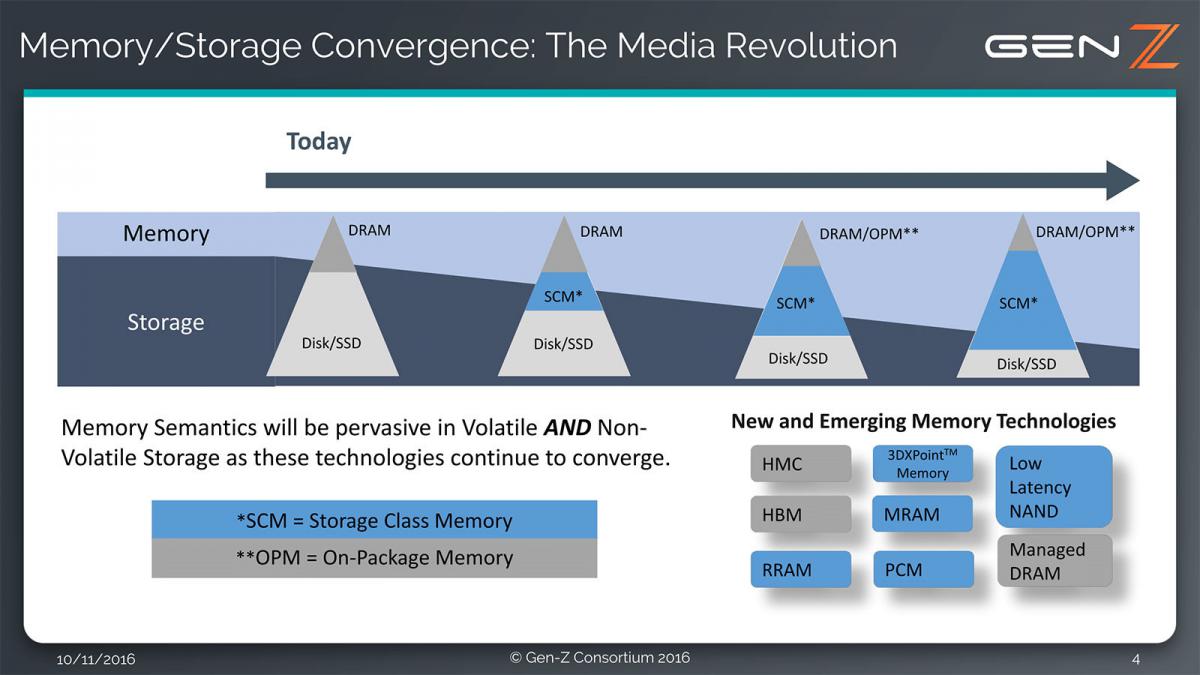

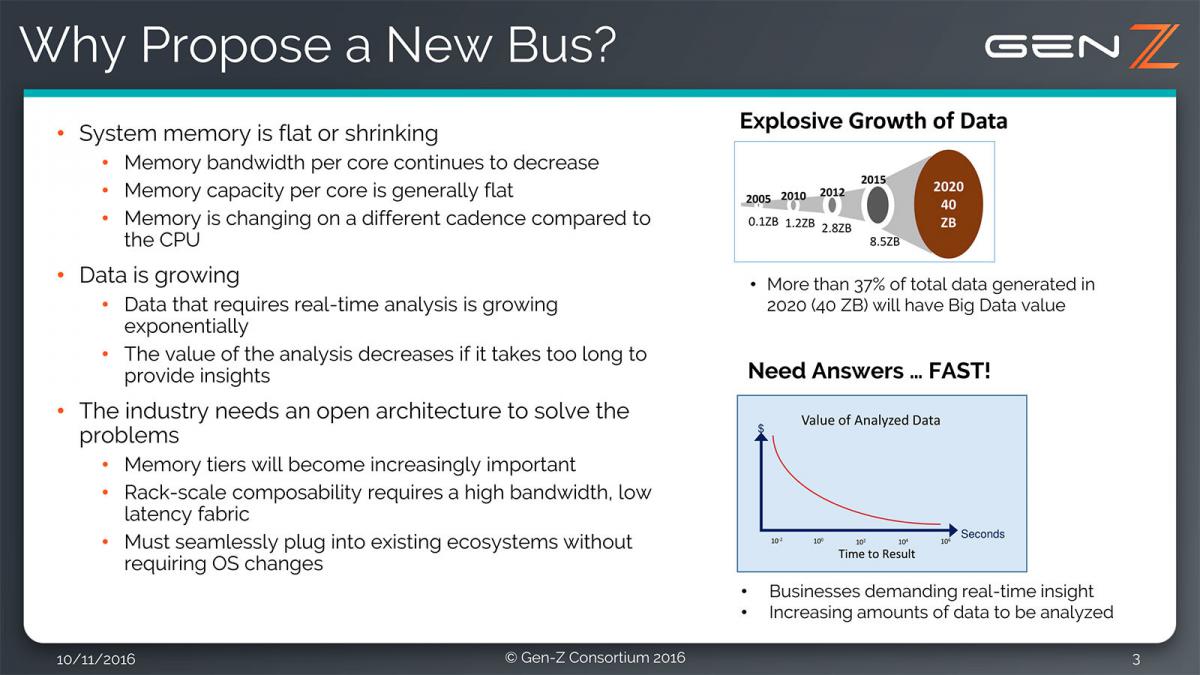

Modern computer systems have been built around the assumption that storage is slow, persistent and reliable, while data in memory is fast but volatile. As new storage class memory technologies emerge that drive the convergence of storage and memory attributes, the programmatic and architectural assumptions that have worked in the past are no longer optimal. The challenges associated with explosive data growth, real-time application demands, the emergence of low latency storage class memory, and demand for rack scale resource pools require a new approach to data access.

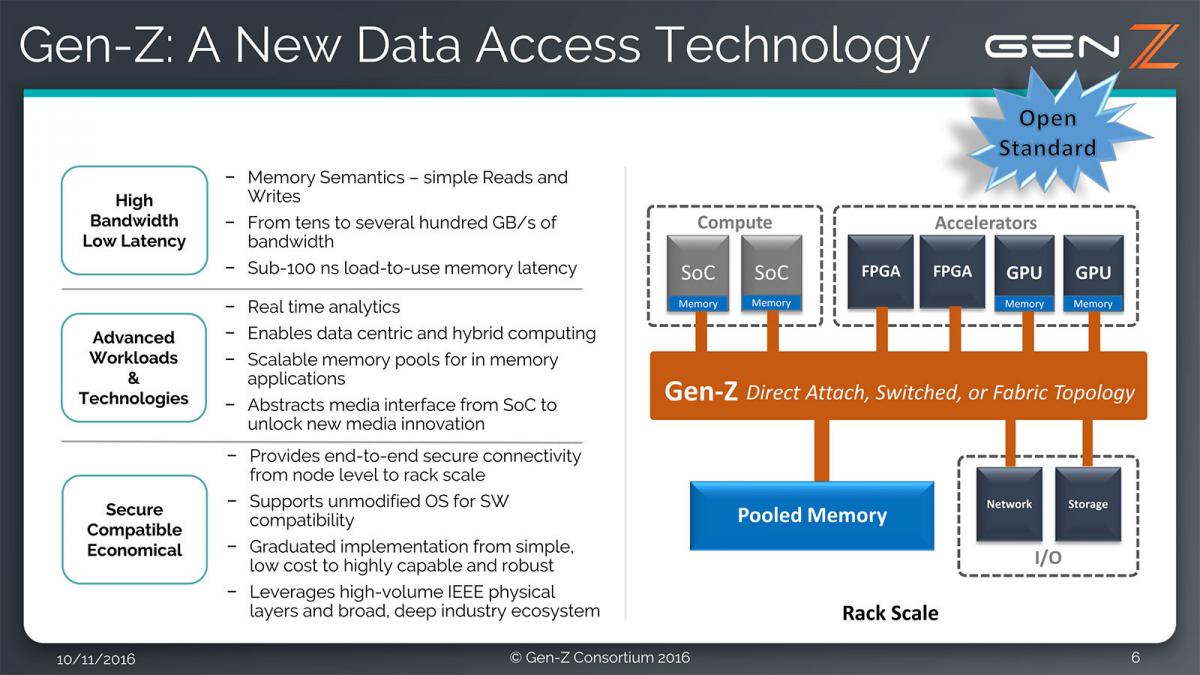

- High Bandwidth, Low Latency: Simplified interface based on memory semantics, scalable from tens to several hundred GB/s of bandwidth, with sub-100 ns load-to-use memory latency.

- Advanced Workloads and Technologies: Enables data centric computing with scalable memory pools and resources for real-time analytics and in-memory applications. Accelerates new memory and storage innovation.

- Compatible and Economical: Highly software compatible with no required changes to the operating system. Scales from simple, low cost connectivity to highly capable, rack scale interconnect.

The Gen-Z Consortium, established by current board members AMD, ARM, Cray, Dell EMC, Hewlett Packard Enterprise (HPE), Huawei, IDT, Micron, Samsung, SK hynix, and Xilinx, is an open, non-proprietary, transparent industry standards body. The consortium reflects a broader industry trend that recognizes the importance of open standards and their role in providing a level playing field to promote adoption, innovation and choice. The Gen-Z Consortium is accepting new members. The core specification, covering the architecture and protocol, will be finalized in late 2016.

“AMD is committed to open ecosystems for technology development and is excited to join the rest of the Gen-Z members today in announcing this significant step. The need for high-bandwidth, low-latency access to memory and storage as well as rack-scale composability in the datacenter is growing rapidly. Gen-Z is an advanced, modern protocol designed to deliver a high-performance, cross-platform solution that can serve its members and their customers far into the future.”

- Mark Papermaster, Chief Technology Officer and Senior Vice President Technology and Engineering, AMD

“Modern data center and cloud workloads drive the need to efficiently integrate emerging memory and storage technologies to solve the challenges at rack-scale. Gen-Z offers a scalable approach to rack-scale sharing, enabling new use cases and system architectures. In concert with other standards bodies, Gen-Z is fostering collaboration between industry leaders to develop open standards that will enable choice and innovation in the data center.”

- Lakshmi Mandyam, Senior Marketing Director of Server Program, ARM

“An open, democratic coherent connectivity standard that enables the next generation of scale and performance is needed in the industry. We are pleased to be a part of the Gen-Z consortium and to contribute to this next phase datacenter architecture. Gen-Z will allow our next generation servers, SoCs and network connectivity products to further accelerate the market trend toward application specific, heterogeneous deployments.”

For more information, visit this page.

Industry Leaders Join Forces to Promote New High-Performance Interconnect and protocol