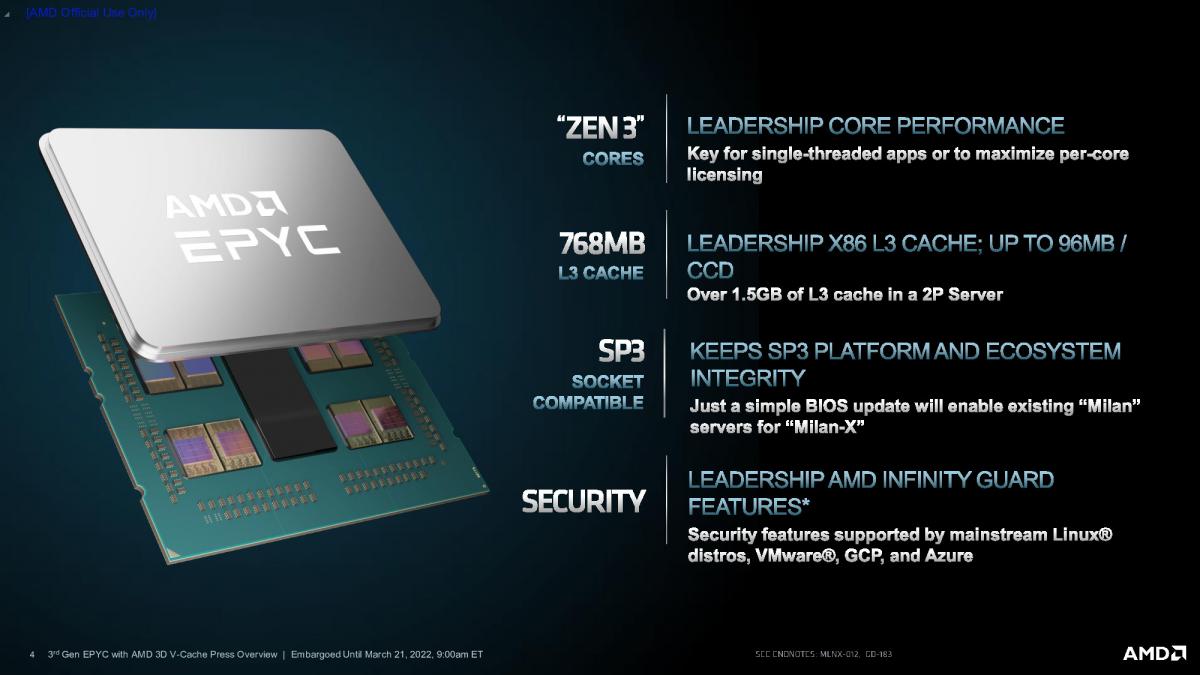

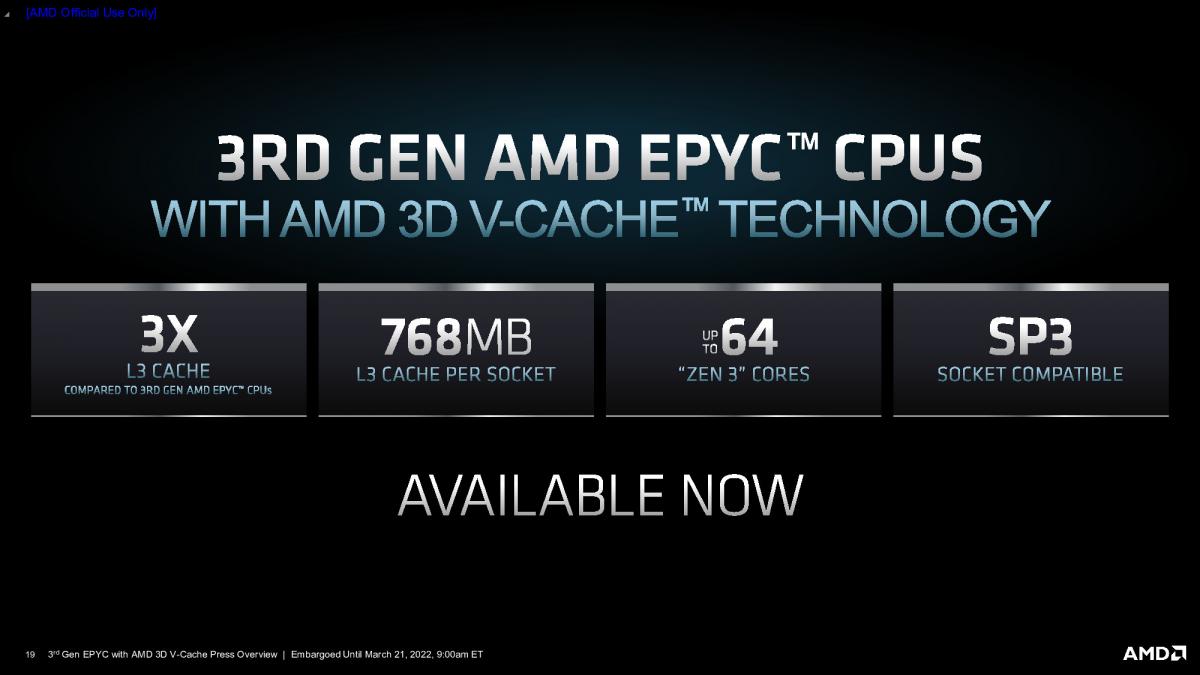

Today, AMD announced the general availability of the world’s first data center CPU using 3D die stacking, the 3rd Gen AMD EPYC processors with AMD 3D V-Cache technology, formerly code-named “Milan-X.” As the highest-performing x86 server CPUs for technical computing, these latest processors deliver the industry’s largest L3 cache, leadership packaging innovation and modern security features.

AMD announced the general availability of the world’s first data center CPU using 3D die stacking, the 3rd Gen AMD EPYC™ processors with AMD 3D V-Cache™ technology, formerly codenamed “Milan-X.” Built on the “Zen 3” core architecture, these processors expand the 3rd Gen EPYC CPU family and can deliver up to 66 percent performance uplift across a variety of targeted technical computing workloads versus comparable, non-stacked 3rd Gen AMD EPYC processors.

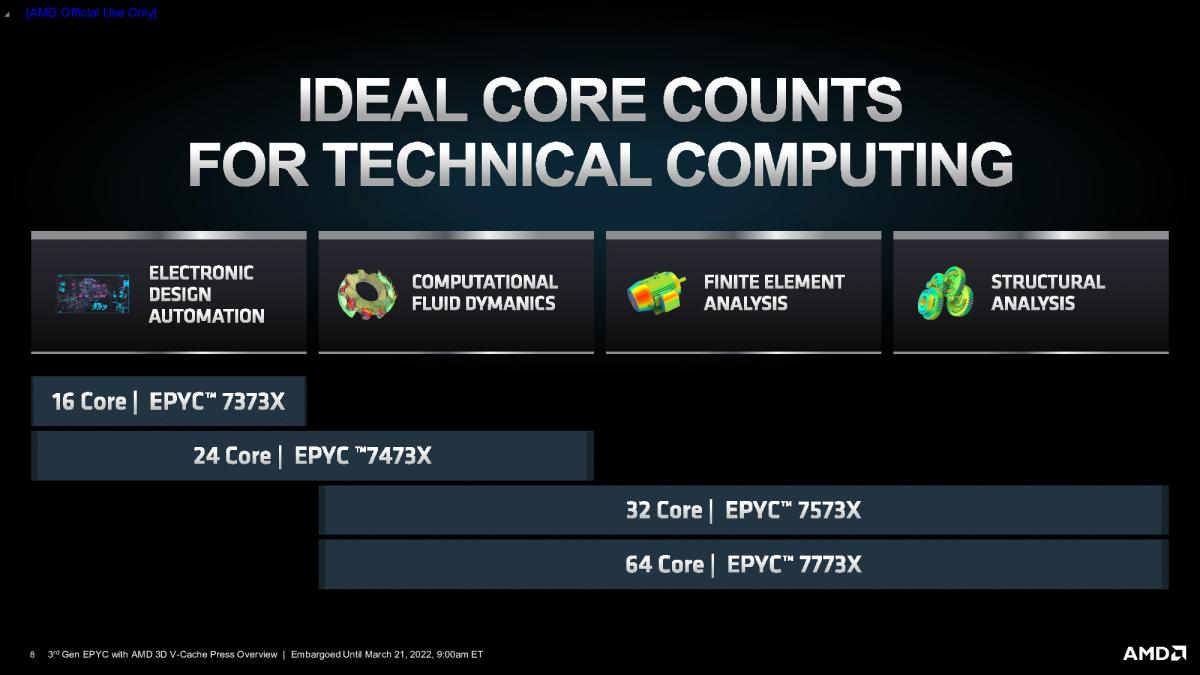

These new processors feature the industry’s largest L3 cache,3 delivering the same socket, software compatibility and modern security features as 3rd Gen EPYC CPUs while providing outstanding performance for technical computing workloads such as computational fluid dynamics (CFD), finite element analysis (FEA), electronic design automation (EDA) and structural analysis. These workloads are critical design tools for companies that must model the complexities of the physical world to create simulations that test and validate engineering designs for some of the world’s most innovate products.

“Building upon our momentum in the data center as well as our history of industry-firsts, 3rd Gen AMD EPYC processors with AMD 3D V-Cache technology showcase our leadership design and packaging technology enabling us to offer the industry’s first workload-tailored server processor with 3D die stacking technology,” said Dan McNamara, senior vice president and general manager, Server Business Unit, AMD. “Our latest processors with AMD 3D V-Cache technology provide breakthrough performance for mission-critical technical computing workloads leading to better designed products and faster time to market.”

“Customers’ increased adoption of data-rich applications requires a new approach to data center infrastructure. Micron and AMD share a vision of delivering full capability of leading DDR5 memory to high-performance data center platforms,” said Raj Hazra, senior vice president and general manager of the Compute and Networking Business Unit at Micron. “Our deep collaboration with AMD includes readying AMD platforms for Micron's latest DDR5 solutions as well as bringing 3rd Gen AMD EPYC processors with AMD 3D V-Cache technology into our own data centers, where we are already seeing up to a 40% performance improvement over 3rd Gen AMD EPYC processors without AMD 3D V-Cache on select EDA workloads.”

Leading Packaging Innovations

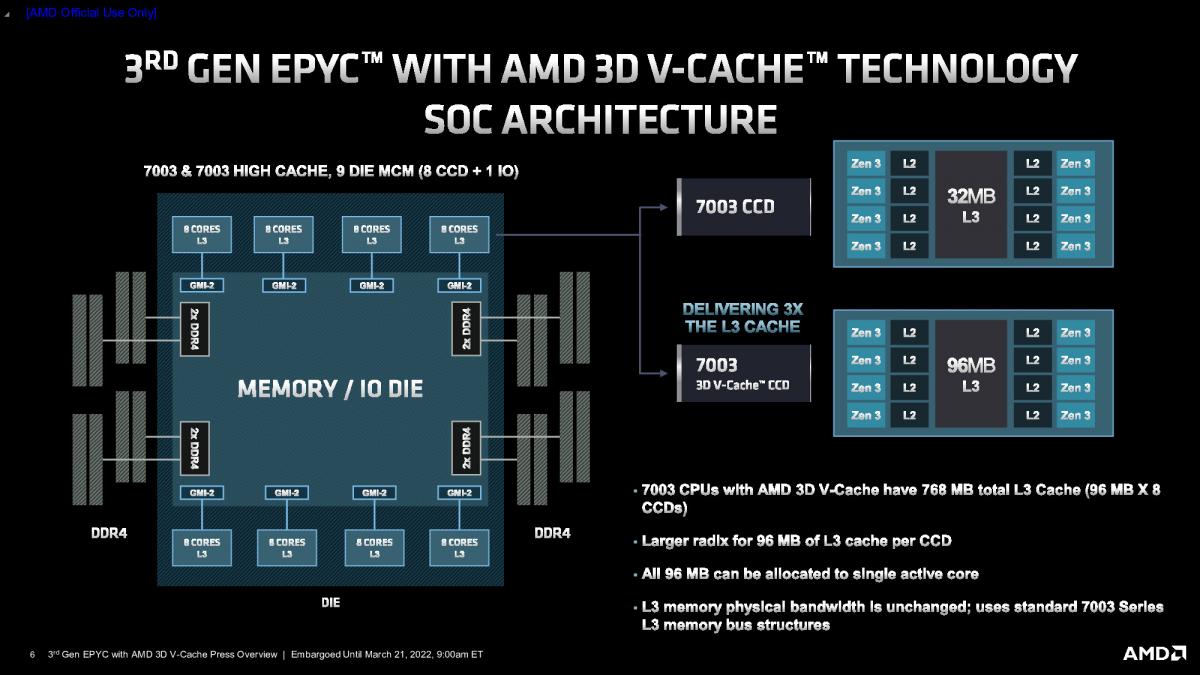

Cache size increases have been at the forefront of performance improvement, particularly for technical computing workloads relying heavily on large data sets. These workloads benefit from increased cache size, however 2D chip designs have physical limitations on the amount of cache that can effectively be built on the CPU. AMD 3D V-Cache technology solves these physical challenges by bonding the AMD “Zen 3” core to the cache module, increasing the amount of L3 while minimizing latency and increasing throughput. This technology represents an innovative step forward in CPU design and packaging and enables breakthrough performance in targeted technical computing workloads.

Breakthrough Performance

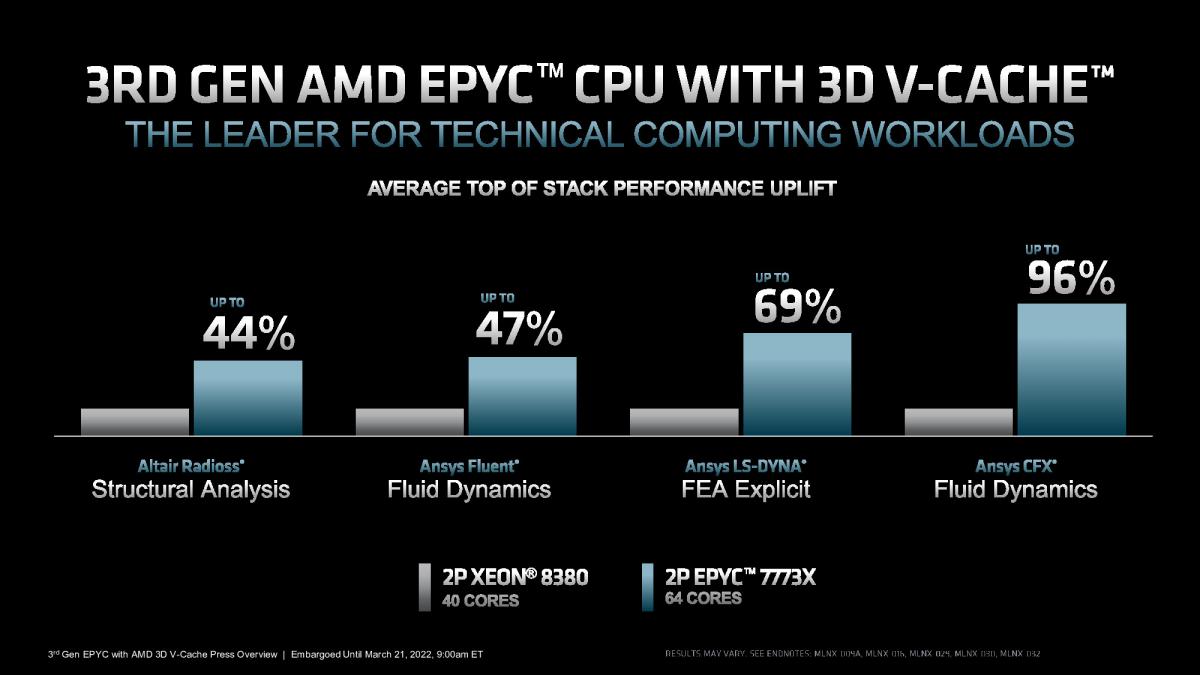

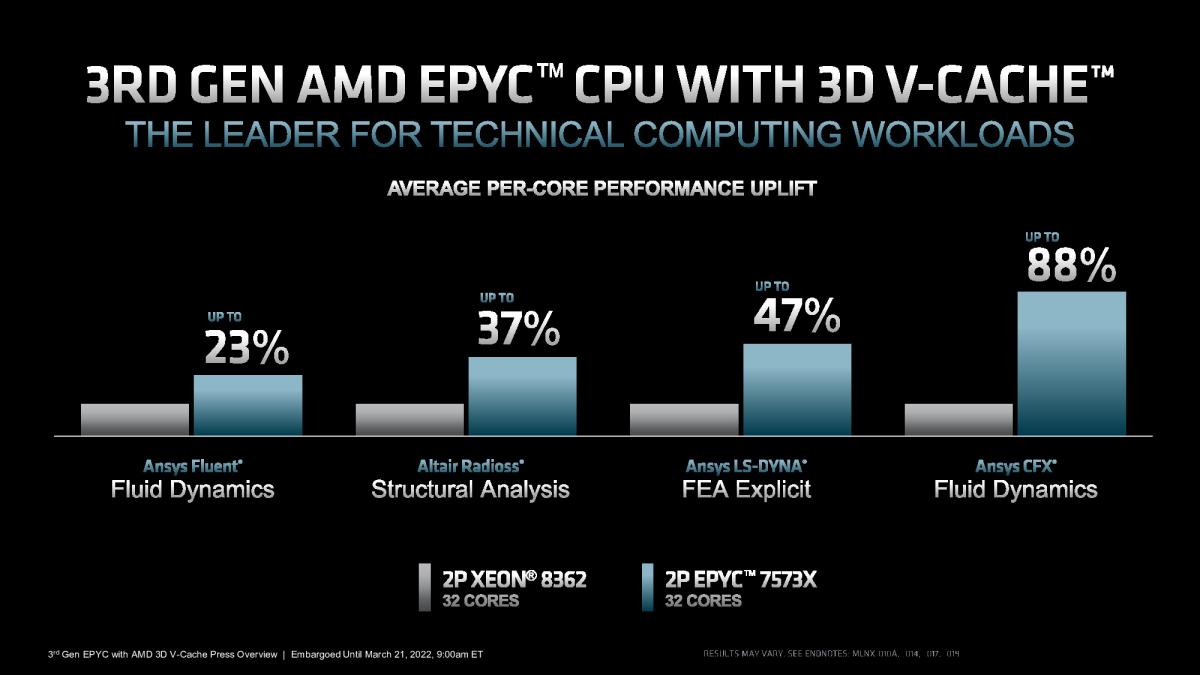

The world’s highest performance server processors for technical computing,4 the 3rd Gen AMD EPYC processors with AMD 3D V-Cache technology deliver faster time-to-results on targeted workloads, such as:

- EDA – The 16-core, AMD EPYC™ 7373X CPU can deliver up to 66 percent faster simulations on Synopsys VCS™, when compared to the EPYC 73F3 CPU.5

- FEA – The 64-core, AMD EPYC 7773X processor can deliver, on average, 44 percent more performance on Altair® Radioss® simulation applications compared to the competition’s top of stack processor.6

- CFD – The 32-core AMD EPYC 7573X processor can solve an average of 88 percent more CFD problems per day than a comparable competitive 32-core count processor, while running Ansys® CFX®.7

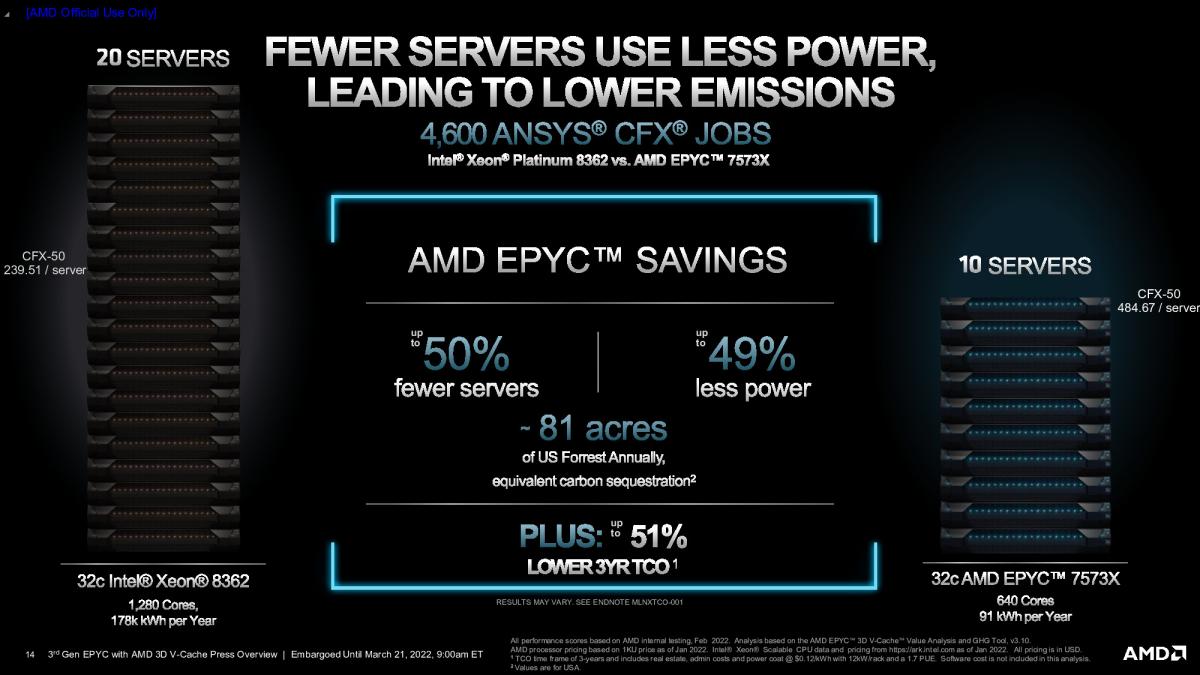

These performance capabilities ultimately enable customers to deploy fewer servers and reduce power consumption in the data center, helping to lower total cost of ownership (TCO), reduce carbon footprint and address their environmental sustainability goals. For instance, in a typical data center scenario running 4600 jobs per day of the Ansys® CFX® test case cfx-50, using 2P 32-core AMD EPYC 7573X CPU based servers can reduce the estimated number of servers required from 20 to 10 and lower power consumption by 49 percent, when compared to the competition’s latest 2P 32-core processor-based server. This ends up providing a projected 51 percent lower TCO over three-years.

In other words, choosing 3rd Gen AMD EPYC processors with AMD 3D V-Cache in this deployment would have the environmental sustainability benefit of more than 81 acres of US forest per year in carbon sequestered equivalents.8

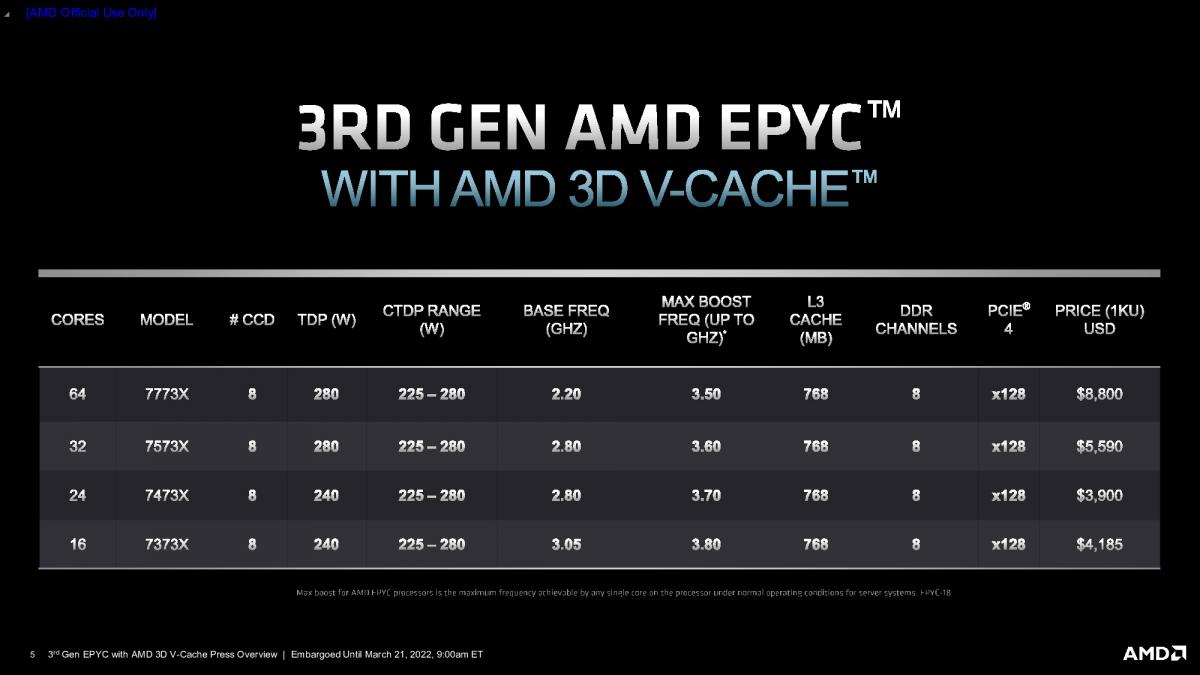

3rd Gen AMD EPYC processor with AMD 3D V-Cache Technology Product Chart

|

Cores |

Model |

# CCD |

TDP (W) |

cTDP range (W) |

Base Freq (GHz) |

Max Boost Freq (Up to GHz)* |

L3 Cache (MB) |

DDR Channels |

Price (1KU) |

|

64 |

7773X |

8 |

280 |

225 – 280 |

2.20 |

3.50 |

768 |

8 |

$ 8,800 |

|

32 |

7573X |

8 |

280 |

225 – 280 |

2.80 |

3.60 |

768 |

8 |

$ 5,590 |

|

24 |

7473X |

8 |

240 |

225 – 280 |

2.80 |

3.70 |

768 |

8 |

$ 3,900 |

|

16 |

7373X |

8 |

240 |

225 – 280 |

3.05 |

3.80 |

768 |

8 |

$ 4,185 |

*Max boost for AMD EPYC processors is the maximum frequency achievable by any single core on the processor under normal operating conditions for server systems.

![2[315762].jpg](https://www.guru3d.com/data/publish/210/493c738a4dd7a62a7729476de07d30115c35c0/2%5B315762%5D.jpg)