The Processor Architecture

Carrizo

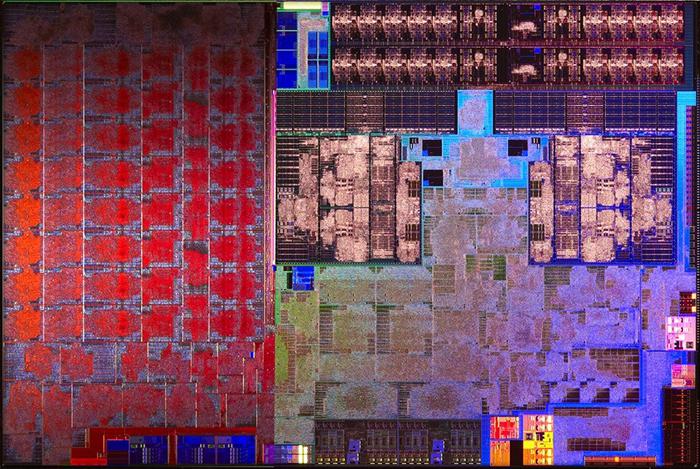

While we will not go intot he technology too deep, the processor is as stated based on Carrizo, with Excavator cores. The chip in fact does have an IGP, but it is disabled for the Athlon X4 845.

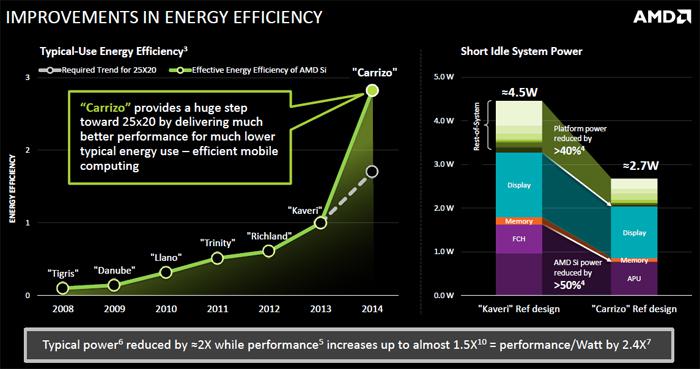

AMD processors have a unique architecture: they have CPU modules, cache, and a discrete-class graphics processor (not active on the 845) all on the same die, using the same bus. Albeit the new architecture resemblesa bit, but isn't. This latest iteration of their mobile APUs will be released in three models, all with updated CPU cores, better graphics performance and an updated video decoder engine that supports HEVC for Ultra HD video. Carrizo is a 28nm process fabbed chip, compared to Intel who is full steam ahead with its 14nm FinFET designs. AMD thinks big and shoots high on the ability to squeeze as much performance per watt out of the larger gate size, before it will shrink processes to 14nm in a later stage.

Processor wise these APUs have been fitted with Excavator CPU cores, Excavator is a micro-architecture under development by AMD to succeed Steamroller. The Carrizo APU is designed to be HSA compliant.

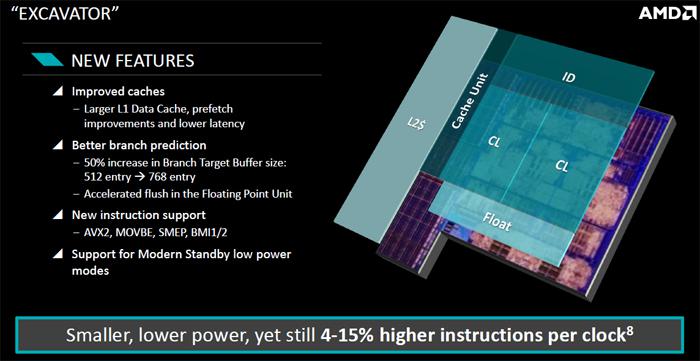

The excavator cores will have support instructions sets such as AVX2, BMI2 and RdRand. For the Excavator series AMD was able to reduce application core by a good 23 per cent, allowing Excavators to run at a higher clock frequency than Steamrollers, yet it will consume roughly the same amount of power. The L2 cache for the cores has been halved to 1MB (compared to kaveri), this creates more die area space for other things. The per-core L1 cache has been doubled to 32KB.

Carrizo should offer many efficiency improvements on evolutionary CPU and GPU architectures. AMD is making bold comparisons, but overall power consumption should be halved compared to last generation products with a perf per watt increase to 2.4x.

Athlon X4 845 comes with up to 4 “Excavator” x86 computing cores arranged as two dual-core units, each tied to 1 MB.

- Support for the latest ISA instructions including FMA4/3, AVX, AES, XOP

- Up to 1MB L2 cache per dual-core module (up to 2MB total)

Inside the processor you'll spot two clusters. Inside the modules we see integer CPU-cores which both share a floating point unit. The L1 instruction cache size was increased to 32KB x4. The L2 cache is 1MB per dual-core module, so that's aMB per core, 2 MB in total so to speak. Basically is is the on-die cache hierarchy:

- L1 Data cache 32KB x4

- L1 Instruction cache 32KBx2

- L2 Cache 1024KBx2

The joint architecture also enables a retained support for security features including FMA4/3, AVX, AES, and XOP. It all comes together into one package that is more than powerful for desktop computing applications, yet does not neglect the essentials required by typical users.