Chief executive officer of Advanced Micro Devices said that the first prototypes of products based on code-named Temash ultra low-power accelerated processing units will be demonstrated around the consumer electronics show next year. Most likely, the demonstrations will be private and made only for partners as the chip will probably be officially launched later in the year.

“[We target] new form-factor clients, low-power clients, tablets. We will launch Temash [based around] Kabini next year, that is a good uptake and you will see some of them around CES time-frame,” said Rory Read, chief executive of AMD, at Credit Suisse Technology Conference, as xbitlabs reports today.

Previously AMD said that it would show off a number of media and business tablets featuring current-generation Z-60 “Hondo” APUs at CES. Those products will most likely go on sale immediately after the first public demonstrations to consumers during the consumer electronics show in early 2013..

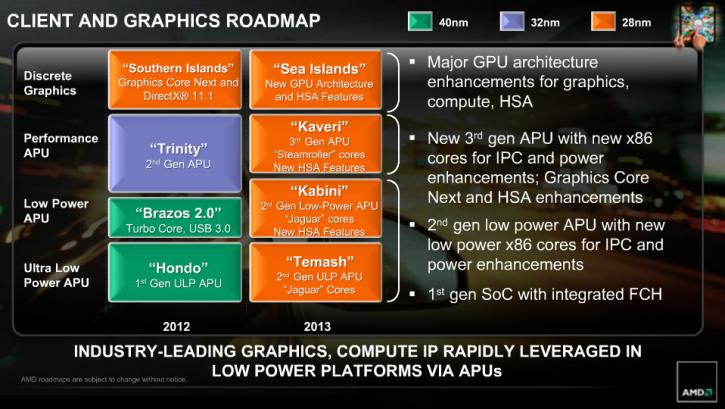

By contrast, devices based on Kabini and/or Temash will reach the market later in 2013, after AMD releases its next-generation APUs and its partners start to mass produce notebooks and tablets on their base.

AMD Kabini will feature up to four x86 cores based on Jaguar micro-architecture, new-generation graphics adapter as well as a number of improvements related to heterogeneous processing and system architecture. Most importantly, Kabini will also integrated input/output capabilities in addition to a new memory controller, which will greatly simplify designs of netbooks, ultra-thin notebooks and other low-power devices. Kabini will generally resemble Temash, but will be tailored for tablets in terms of performance and power consumption. Kabini and Temash will be made using 28nm process technology.

In order to significantly improve performance of Jaguar-based APUs over the Bobcat-powered chips, AMD decided to go into virtually all logical directions: increase the amount of cores, boost clock-speed, add support for modern instructions, increase amount of executed instructions per clock (IPC). AMD also decided to improve power efficiency through clock gating and unit redesign in a bid to ensure lower idle power consumption compared to existing low-power designs. Jaguar features SSE4.1, SSE4.2, AES, PCLMUL, AVX, BMI, F16C as well as MOVBE. Jaguar also introduces 128-bit floating point unit (FPU) with enhancements and double-pumping to support 256-bit AVX instructions as well as an innovative integer unit with new hardware divider, larger schedulers and more out-of-order resources. AMD implemented a new CC6 state with even deeper energy economy, with each core able to go there independently.

.jpg)