The Architecture - Cache - Compilers - processors

The Architecture

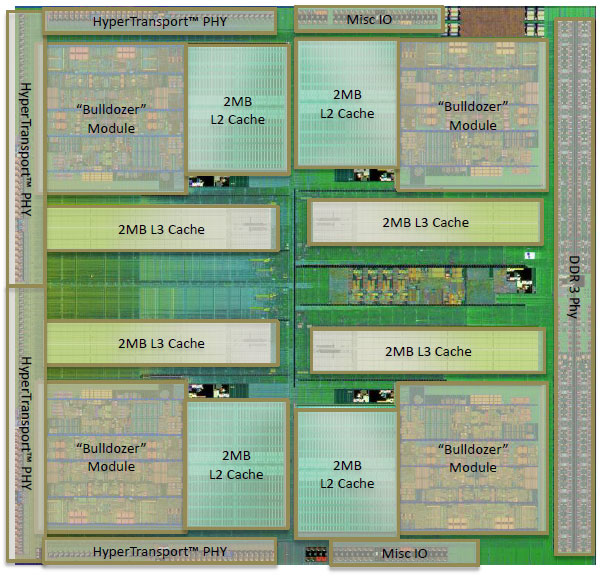

The new FX series processors have been built upon what you guys know as the Zambezi architecture, all managed on the 32nm fabrication node. Each Zambezi processor will have Bulldozer units, or segmented modules. I can explain this very simply, one Bulldozer module is two logical AMD64 CPU cores tied together. With four Bulldozer modules you thus get eight logical CPU cores. Have a peek at the die photo below where you will understand it more easily after observing.

The roughly 1.2 Billion transistor count FX-8150 processor tested today thus has four Bulldozer modules, each of which contains two AMD64 cores, and an integrated memory controller.

Different though in this new design is that each module shares several components including a front-end (fetch and decode), floating-point unit, data prefetch unit, and 2MB of L2 cache. The shared Bulldozer modules made it possible to group more cores on a smaller die and boost the horsepower of the floating-point unit, so that is all about gaining as much efficiency as possible.

You can understand it's also very modular, AMD could make 2,4,6,8,10,12,14,16 and so on core processors when the time is right and the technology allows it. It is a very scalable base design.

The eight-core Bulldozer processor is manufactured by GlobalFoundries on its 32nm SOI (Silicon-On-Insulator) process. Like the A-Series APUs for mainstream laptops, it measures 315 square millimeters and has roughly 1.2 Billion transistors.

The Caches

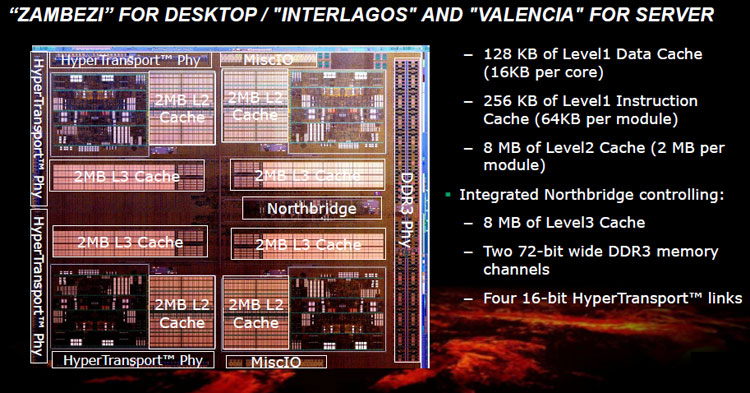

Caches then; there are significant changes here opposed to Phenom II and Athlon II alright. Each CPU core has 128 KB of Level 1 Cache, 16 KB/Core, a 64-byte cacheline, 4-way associative, write-through. Then there is 8 MB of Level 2 Cache, 2 MB per Bulldozer module, a 64-byte cacheline, 16-way associative.

Then there is a third cache. AMD has designed a shared 8 MB L3 cache with 64 way associatively for both cores in a Bulldozer module. Each Bulldozer unit (each two cores) have 2 MB L3 cache. Each module can access the entirety of the 8MB L3, although cache partitioning happens on a core & thread generation basis so its virtually impossible for one core to get allocated the full 8MB of L3.

New Instruction sets (compilers)

Bulldozer has several new instructions including some that are in both AMD and Intel processors (SSE, encryption, and AVX for floating-point operations) and some unique to AMD that fill in some holes including FMA4 for HPC applications and XOP for numeric, multimedia, and audio/radio applications.

The Processors

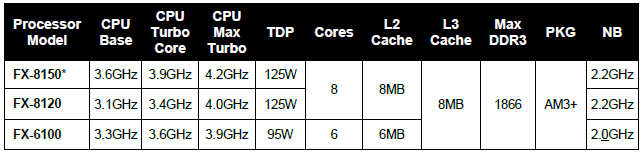

So once more, to get you a little clarity -- the top of the range part, FX-8150, is clocked at 3.6 GHz, with a TDP of 125W. Next in line is the FX-8120, clocked at 3.1 GHz. There are two versions - 125W and 95W. This suggests that the FX-8120 was initially targeted for 95W but may ship with a 125W TDP to begin with. The final 8-core CPU is the FX-8100, clocked at 2.8 GHz.

The sole 6-core CPU will be FX-6100 at 3.3 GHz while the 4-core CPU will be FX-4100 clocked at 3.6 GHz. Both feature 95W TDP, and will likely compete up against the Core i5 series. All CPUs feature 8MB L3 cache. This suggests that FX-6100 and FX-4100 are likely to be Zambezi with 1 module and 2 modules disabled, respectively, rather than native 3-module / 2-module dies.

Released today however are: